День добрый всем.

Не пинайте сразу, только начал освоение VHDL, а спросить не у кого.

Работаю в Active HDL 10.2.

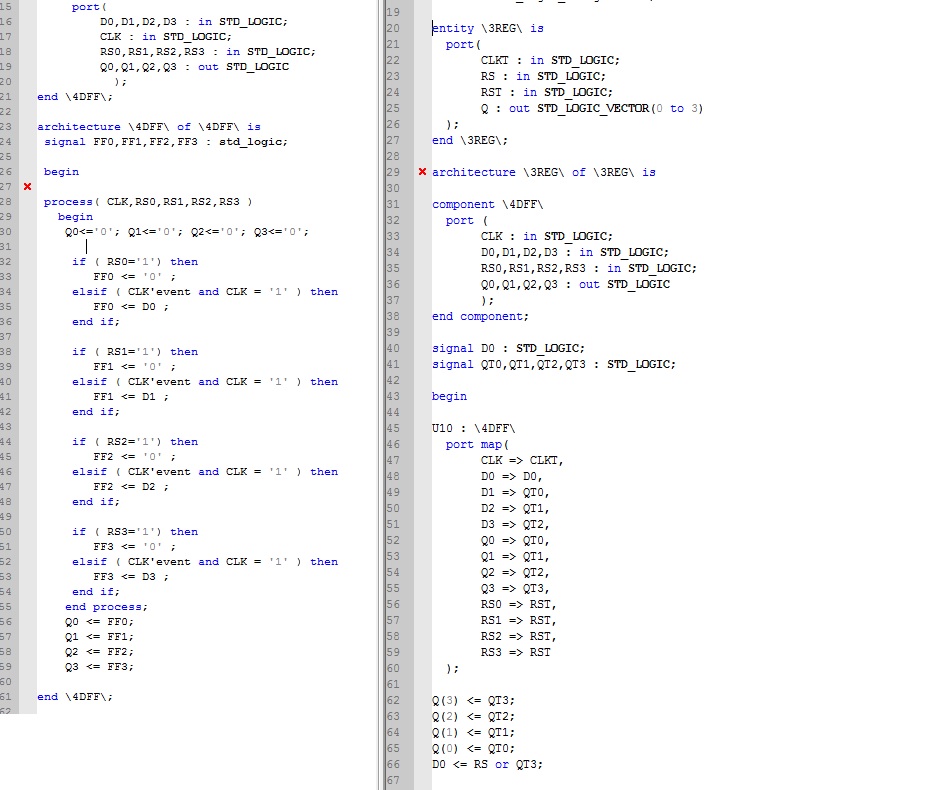

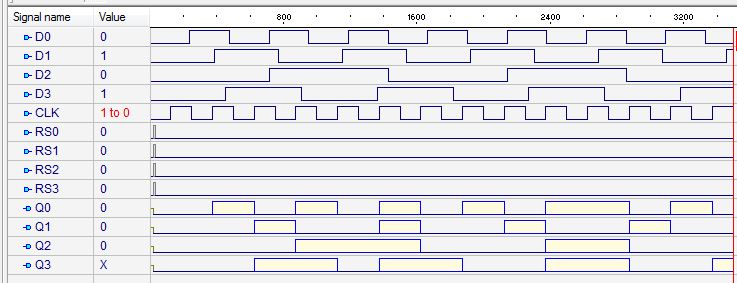

Проблема такая : создал компонент - синхронный счетверённый Д-триггер с общим клоком, всё компилируется и работает.

Создаю в том же проекте другой компонент - в основе тот-же 4-Д-триггер с обвеской простой логикой - всё компилится, но при симуляции - неопределённое состояние выходов, т.е. не работает.

В чём может быть ошибка? вроде же создают многокомпонентные схемы? или надо другой проект создавать и в него добавлять компонент?

Полная версия этой страницы: Не работает схема верхнего уровня

Форум разработчиков электроники ELECTRONIX.ru > Программируемая логика ПЛИС (FPGA,CPLD, PLD) > Языки проектирования на ПЛИС (FPGA)

Телепаты уже в летних отпусках. Покажите код.

Приветствую!

Ну и кто за Вас будет ресетить логику в начале симуляции?.

По умолчанию все регистры при старте симуляции ставятся в U состояние (в отличии от реального железа) - это помогает при разработку отслеживать некорректную инициализацию дизайна.

Удачи! Rob.

Да там особо нет текста

Вот ещё схема для понимания

Вот ещё схема для понимания

Ну и кто за Вас будет ресетить логику в начале симуляции?.

По умолчанию все регистры при старте симуляции ставятся в U состояние (в отличии от реального железа) - это помогает при разработку отслеживать некорректную инициализацию дизайна.

Удачи! Rob.

Приветствую!

Ну и кто за Вас будет ресетить логику в начале симуляции?.

По умолчанию все регистры при старте симуляции ставятся в U состояние (в отличии от реального железа) - это помогает при разработку отслеживать некорректную инициализацию дизайна.

Удачи! Rob.

Ну и кто за Вас будет ресетить логику в начале симуляции?.

По умолчанию все регистры при старте симуляции ставятся в U состояние (в отличии от реального железа) - это помогает при разработку отслеживать некорректную инициализацию дизайна.

Удачи! Rob.

Ресет отключен пока в процессе отладки, по логике схема должна работать примерно так:

с 1 тактом первый триггер принимает состояние 1

со 2 тактом - второй 1, первый ноль, и т.д.

бегающая единичка

Ресет отключен пока в процессе отладки, по логике схема должна работать примерно так:

с 1 тактом первый триггер принимает состояние 1

со 2 тактом - второй 1, первый ноль, и т.д.

бегающая единичка

с 1 тактом первый триггер принимает состояние 1

со 2 тактом - второй 1, первый ноль, и т.д.

бегающая единичка

Добавил сброс вместо земли - не поменялось

Приветствую!

Один из этих вариантов Вы и видите.

Не надейтесь на удачу (даже наоборот - ожидайте неприятностей) - и делайте так чтобы всегда быть уверенным в контроле состояния дизайна.

P.S. Какой тощий сброс аш жалко. На тригграх ресет какой ? асинхронный или синхронный?

аш жалко. На тригграх ресет какой ? асинхронный или синхронный?

Удачи! Rob.

Ресет отключен пока в процессе отладки, по логике схема должна работать примерно так:

...

Это понятно что по логику - но по факту я вижу схему которая может работать (в симе) как минимум 17-ю разными вариантами в зависимости от того как изначально инициализируются регистры. ...

Один из этих вариантов Вы и видите.

Не надейтесь на удачу (даже наоборот - ожидайте неприятностей) - и делайте так чтобы всегда быть уверенным в контроле состояния дизайна.

P.S. Какой тощий сброс

Удачи! Rob.

Приветствую!

Это понятно что по логику - но по факту я вижу схему которая может работать (в симе) как минимум 17-ю разными вариантами в зависимости от того как изначально инициализируются регистры.

Один из этих вариантов Вы и видите.

Не надейтесь на удачу (даже наоборот - ожидайте неприятностей) - и делайте так чтобы всегда быть уверенным в контроле состояния дизайна.

P.S. Какой тощий сброс аш жалко. На тригграх ресет какой ? асинхронный или синхронный?

аш жалко. На тригграх ресет какой ? асинхронный или синхронный?

Удачи! Rob.

Это понятно что по логику - но по факту я вижу схему которая может работать (в симе) как минимум 17-ю разными вариантами в зависимости от того как изначально инициализируются регистры.

Один из этих вариантов Вы и видите.

Не надейтесь на удачу (даже наоборот - ожидайте неприятностей) - и делайте так чтобы всегда быть уверенным в контроле состояния дизайна.

P.S. Какой тощий сброс

Удачи! Rob.

Простой триггер:

if ( RS='1') then

FF <= '0' ;

elsif ( CLK'event and CLK = '1' ) then

FF <= D after 1 ns ;

end if;

Простой триггер:

if ( RS='1') then

FF <= '0' ;

elsif ( CLK'event and CLK = '1' ) then

FF <= D after 1 ns ;

end if;

if ( RS='1') then

FF <= '0' ;

elsif ( CLK'event and CLK = '1' ) then

FF <= D after 1 ns ;

end if;

Во-первых

Код

after 1 ns;

не синтезируется.Во-вторых у вас триггер никак не инициализирован.

Либо вручную при объявлении сигнала (или порта) присвойте начальное значение, либо сначала сбрасывайте триггер. Хотя это Вам говорили. Что Вы ещё хотите услышать я не знаю.

Примерно понял.

Но, в примерах триггера не делают предварительную установку значения, и всё работает..

И получается что сигнал сброса, генерируемый в начале тестирования, не устанавливает в ноль, а надо делать заранее установку?

Но, в примерах триггера не делают предварительную установку значения, и всё работает..

И получается что сигнал сброса, генерируемый в начале тестирования, не устанавливает в ноль, а надо делать заранее установку?

Приветстувую!

Это значит что у Вас что то не так либо с сигналом сброса либо с описанием триггера.

Попробуйте сделать сброс шириной в пару тактов CLK, Ну и описание триггера целиком покажите.

Удачи! Rob.

Примерно понял.

Но, в примерах триггера не делают предварительную установку значения, и всё работает..

И получается что сигнал сброса, генерируемый в начале тестирования, не устанавливает в ноль, а надо делать заранее установку?

Но, в примерах триггера не делают предварительную установку значения, и всё работает..

И получается что сигнал сброса, генерируемый в начале тестирования, не устанавливает в ноль, а надо делать заранее установку?

Это значит что у Вас что то не так либо с сигналом сброса либо с описанием триггера.

Попробуйте сделать сброс шириной в пару тактов CLK, Ну и описание триггера целиком покажите.

Удачи! Rob.

Примерно понял.

Но, в примерах триггера не делают предварительную установку значения, и всё работает..

Но, в примерах триггера не делают предварительную установку значения, и всё работает..

Потому-что многим триггерам предварительная установка не требуется.

Например есть выход 8-разрядного регистра data_out. И есть сигнал валидности этих данных data_valid.

Так вот начальная установка регистра data_out не требуется. А вот сигнал валидности data_valid желательно как-либо установить в начальное значение. Либо путем начального сброса, либо начальной установкой схемы.

Более того не все FPGA поддерживают возможность начальной установки значения, на сколько я помню FPGA фирмы Actel не умеют инициализировать триггеры каким-то значением. А некоторые FPGA могут затребовать дополнительных ресурсов для начальной установки значения. Например в чипах Altera cyclone C5SEMA5F31C6 установка начального значения триггера в нули - ресурсов не требует. А вот установка в единицы - требует дополнительный слой логики, что может иметь значение на проектах, критичных к максимальным частотам.

Цитата

И получается что сигнал сброса, генерируемый в начале тестирования, не устанавливает в ноль, а надо делать заранее установку?

Не так. Правильно сделанный сброс - устанавливает значение триггера в то значение, в которое Вы его сбрасываете. Ключевая фраза - правильно сделанный сброс. А как делать правильно - зависит от проекта. У меня обычно присутствует начальный сброс.

Хорошо, но в данном случае что надо первоначально обнулять? D0...3? Q0...3? FF0...3?

Приветствую!

Ресетить всегда нужно источник сигнала. Что является источником в Вашей схеме? - выход триггеров.

Еще раз повторю - если при подачи на вход сброса RS Ваш триггер не сбрасывается - это значит что что то не так и дальнейшие гадания ни к чему не приведут. Надо для начала разобраться с одним триггером - почему он не сбрасывается?

Просимулируйте один триггер - выведите на диаграмму все сигналы из с него (или изнутри 4DF) и посмотрите что и как.

Судя по куску кода триггера он асинхронный - может Вы не добавили RS в список чувствительности процесса?

P.S. Ну и когда с триггером разберетесь - ресет дизайна нужно делать так чтобы всегда приводить схему в нужное состояние - в Вашей схеме это не так - от ширины импульса на входе RST будет зависть что запишется в регистр и соответственно бегущую единицу Вы получите не всегда.

Удачи! Rob.

Хорошо, но в данном случае что надо первоначально обнулять? D0...3? Q0...3? FF0...3?

Ресетить всегда нужно источник сигнала. Что является источником в Вашей схеме? - выход триггеров.

Еще раз повторю - если при подачи на вход сброса RS Ваш триггер не сбрасывается - это значит что что то не так и дальнейшие гадания ни к чему не приведут. Надо для начала разобраться с одним триггером - почему он не сбрасывается?

Просимулируйте один триггер - выведите на диаграмму все сигналы из с него (или изнутри 4DF) и посмотрите что и как.

Судя по куску кода триггера он асинхронный - может Вы не добавили RS в список чувствительности процесса?

P.S. Ну и когда с триггером разберетесь - ресет дизайна нужно делать так чтобы всегда приводить схему в нужное состояние - в Вашей схеме это не так - от ширины импульса на входе RST будет зависть что запишется в регистр и соответственно бегущую единицу Вы получите не всегда.

Удачи! Rob.

Хорошо, но в данном случае что надо первоначально обнулять? D0...3? Q0...3? FF0...3?

У вас внутренние состояния регистров U - т.е. неопределены, и из-за того, что на первый из регистров подается выход последнего прооренный со входным сигналом, это самое неопределенное состояние так и будет бесконечно на выходе каждого из регистров. Выше вам уже правильно посоветовали либо задать изначальные состояния этих самых регистров, либо устанавливать их по сбросу.

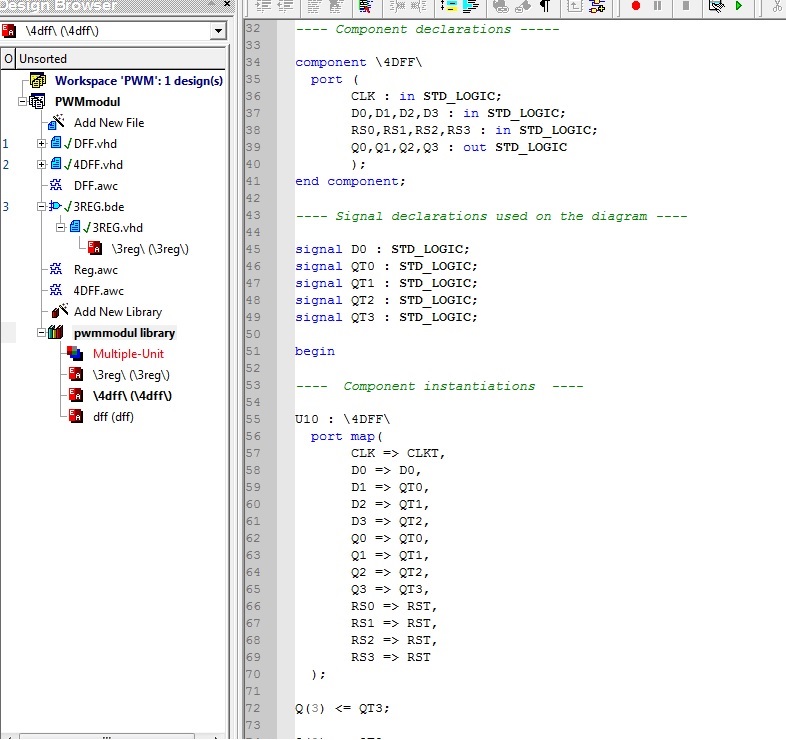

И вопрос остался - надо делать отдельный проект для каждого уровня или в одном можно, сейчас вот так

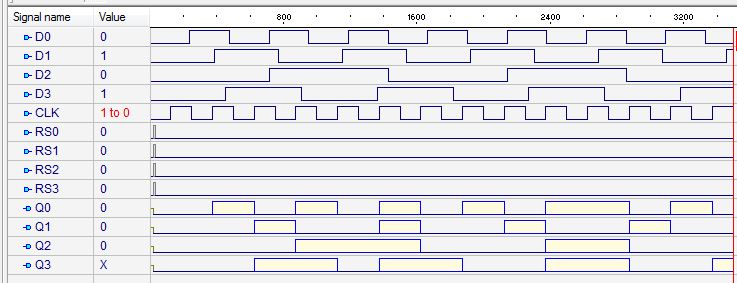

Вот симуляция триггера - всё работает

То есть если на элемент ИЛИ на один вход подаётся 1 а другой - неопределённый - логика не сработает?

Приветствую!

Ресетить всегда нужно источник сигнала. Что является источником в Вашей схеме? - выход триггеров.

Еще раз повторю - если при подачи на вход сброса RS Ваш триггер не сбрасывается - это значит что что то не так и дальнейшие гадания ни к чему не приведут. Надо для начала разобраться с одним триггером - почему он не сбрасывается?

Просимулируйте один триггер - выведите на диаграмму все сигналы из с него (или изнутри 4DF) и посмотрите что и как.

Судя по куску кода триггера он асинхронный - может Вы не добавили RS в список чувствительности процесса?

P.S. Ну и когда с триггером разберетесь - ресет дизайна нужно делать так чтобы всегда приводить схему в нужное состояние - в Вашей схеме это не так - от ширины импульса на входе RST будет зависть что запишется в регистр и соответственно бегущую единицу Вы получите не всегда.

Удачи! Rob.

Ресетить всегда нужно источник сигнала. Что является источником в Вашей схеме? - выход триггеров.

Еще раз повторю - если при подачи на вход сброса RS Ваш триггер не сбрасывается - это значит что что то не так и дальнейшие гадания ни к чему не приведут. Надо для начала разобраться с одним триггером - почему он не сбрасывается?

Просимулируйте один триггер - выведите на диаграмму все сигналы из с него (или изнутри 4DF) и посмотрите что и как.

Судя по куску кода триггера он асинхронный - может Вы не добавили RS в список чувствительности процесса?

P.S. Ну и когда с триггером разберетесь - ресет дизайна нужно делать так чтобы всегда приводить схему в нужное состояние - в Вашей схеме это не так - от ширины импульса на входе RST будет зависть что запишется в регистр и соответственно бегущую единицу Вы получите не всегда.

Удачи! Rob.

Вот симуляция триггера - всё работает

У вас внутренние состояния регистров U - т.е. неопределены, и из-за того, что на первый из регистров подается выход последнего прооренный со входным сигналом, это самое неопределенное состояние так и будет бесконечно на выходе каждого из регистров. Выше вам уже правильно посоветовали либо задать изначальные состояния этих самых регистров, либо устанавливать их по сбросу.

То есть если на элемент ИЛИ на один вход подаётся 1 а другой - неопределённый - логика не сработает?

Приветствую!

Ну теперь понятнее - судя по всему у Вас что то с выходами Q - как они в TB подключенны ?

Поэтому вместо 1 выход триггеров в X переключается - кофликтует с другим источником на Q.

Давно в Aledc не работал - но насколько помню можете выбрать любой файл в иерархии и сгенерировать для него TB в том же самом проекте.

В доке Aldec или в сети можно (и нужно) найти табличку результата логических операций в зависимости от типа сигналов (0,1,X,U...).

Удачи! Rob.

И вопрос остался - надо делать отдельный проект для каждого уровня или в одном можно, сейчас вот так

...

Вот симуляция триггера - всё работает

...

То есть если на элемент ИЛИ на один вход подаётся 1 а другой - неопределённый - логика не сработает?

...

Вот симуляция триггера - всё работает

...

То есть если на элемент ИЛИ на один вход подаётся 1 а другой - неопределённый - логика не сработает?

Ну теперь понятнее - судя по всему у Вас что то с выходами Q - как они в TB подключенны ?

Поэтому вместо 1 выход триггеров в X переключается - кофликтует с другим источником на Q.

Давно в Aledc не работал - но насколько помню можете выбрать любой файл в иерархии и сгенерировать для него TB в том же самом проекте.

В доке Aldec или в сети можно (и нужно) найти табличку результата логических операций в зависимости от типа сигналов (0,1,X,U...).

Удачи! Rob.

Потому-что начальное значение задается в области декларации сигнала

Например:

И вообще. Я боюсь представить себе, как бы у Вас выглядел 256 битный регистр...

Например:

Код

architecture RTL of testing

signal shreg : std_logic_vector(2 downto 0) := (others => '0'); -- вот тут задаем начальное значние !

begin

signal shreg : std_logic_vector(2 downto 0) := (others => '0'); -- вот тут задаем начальное значние !

begin

И вообще. Я боюсь представить себе, как бы у Вас выглядел 256 битный регистр...

Приветствую!

Правая часть генерируется автоматом из вашей схемы. Там нет сигналов из которых получается "триггеры" - только соединения - Добавлять какую либо инициализацию туда бессмыслено.

Покажите лучше TB для модуля 3REG

Удачи! Rob.

Добавил установку в триггер, но теперь вопрос - где делать установку в правой программе? Потому что не повлияло на работу обнуление триггера в правой.

...

...

Правая часть генерируется автоматом из вашей схемы. Там нет сигналов из которых получается "триггеры" - только соединения - Добавлять какую либо инициализацию туда бессмыслено.

Покажите лучше TB для модуля 3REG

Удачи! Rob.

Потому-что начальное значение задается в области декларации сигнала

Например:

И вообще. Я боюсь представить себе, как бы у Вас выглядел 256 битный регистр...

Например:

Код

architecture RTL of testing

signal shreg : std_logic_vector(2 downto 0) := (others => '0'); -- вот тут задаем начальное значние !

begin

signal shreg : std_logic_vector(2 downto 0) := (others => '0'); -- вот тут задаем начальное значние !

begin

И вообще. Я боюсь представить себе, как бы у Вас выглядел 256 битный регистр...

Регистры инициализировались.но ..не работают..

А разработка планируется чтобы не использовать 3 1024-битных регистра)))

Приветствую!

Правая часть генерируется автоматом из вашей схемы. Там нет сигналов из которых получается "триггеры" - только соединения - Добавлять какую либо инициализацию туда бессмыслено.

Покажите лучше TB для модуля 3REG

Удачи! Rob.

Правая часть генерируется автоматом из вашей схемы. Там нет сигналов из которых получается "триггеры" - только соединения - Добавлять какую либо инициализацию туда бессмыслено.

Покажите лучше TB для модуля 3REG

Удачи! Rob.

А разве вставленный блок 4DFF не должен выполнять функцию логики?

Я так понимаю у меня где-то должна появиться функция process(CLK,RS,RST)

Внесу свои пять копеек.

Первое, из-за чего код нерабочий: сигналы Q0...Q3 присваиваются одновременно внутри процесса и вне его. Симулятор создаст для них по два драйвера один - в '0' по изменению любого сигнала из списка чувствительности, второй - в значение сигналов FF0...FF3. В результате при моделировании получите либо '0', либо 'X'. Про синтез пока даже говорить не стоит.

Cудя по коду вы хотите сделать схему, в которой '1' циклически бегает по выхохам Q0...Q3. Сдвиг вы описали, зацикливание тоже. Осталось задать то, что должно там крутиться. Например, сразу по сбросу выставить схему в одно из устраивающих вас состояний. Потом посмОтрите, как вы будете это все рушить своим входным сигналом.

Первое, из-за чего код нерабочий: сигналы Q0...Q3 присваиваются одновременно внутри процесса и вне его. Симулятор создаст для них по два драйвера один - в '0' по изменению любого сигнала из списка чувствительности, второй - в значение сигналов FF0...FF3. В результате при моделировании получите либо '0', либо 'X'. Про синтез пока даже говорить не стоит.

Cудя по коду вы хотите сделать схему, в которой '1' циклически бегает по выхохам Q0...Q3. Сдвиг вы описали, зацикливание тоже. Осталось задать то, что должно там крутиться. Например, сразу по сбросу выставить схему в одно из устраивающих вас состояний. Потом посмОтрите, как вы будете это все рушить своим входным сигналом.

Внесу свои пять копеек.

Первое, из-за чего код нерабочий: сигналы Q0...Q3 присваиваются одновременно внутри процесса и вне его. Симулятор создаст для них по два драйвера один - в '0' по изменению любого сигнала из списка чувствительности, второй - в значение сигналов FF0...FF3. В результате при моделировании получите либо '0', либо 'X'. Про синтез пока даже говорить не стоит.

Cудя по коду вы хотите сделать схему, в которой '1' циклически бегает по выхохам Q0...Q3. Сдвиг вы описали, зацикливание тоже. Осталось задать то, что должно там крутиться. Например, сразу по сбросу выставить схему в одно из устраивающих вас состояний. Потом посмОтрите, как вы будете это все рушить своим входным сигналом.

Первое, из-за чего код нерабочий: сигналы Q0...Q3 присваиваются одновременно внутри процесса и вне его. Симулятор создаст для них по два драйвера один - в '0' по изменению любого сигнала из списка чувствительности, второй - в значение сигналов FF0...FF3. В результате при моделировании получите либо '0', либо 'X'. Про синтез пока даже говорить не стоит.

Cудя по коду вы хотите сделать схему, в которой '1' циклически бегает по выхохам Q0...Q3. Сдвиг вы описали, зацикливание тоже. Осталось задать то, что должно там крутиться. Например, сразу по сбросу выставить схему в одно из устраивающих вас состояний. Потом посмОтрите, как вы будете это все рушить своим входным сигналом.

Да, предполагается потом на логике реализовать чтобы при сбросе всё выставлялось в ноль, а младший регистр в 1, которая при каждом следующем клоке будет сдвигаться в следующий разряд и переходить в нулевой через или, при этом схема не будет зависеть от количества триггеров (сейчас 4 потом хоть 10) а обнуление приходится делать чтобы не было неопределённых значений.

И можжно ссылку на номера строк листинга где двойное присваивание?

младший регистр в 1

Вот этого пока не описано. А стоило бы.

а обнуление приходится делать чтобы не было неопределённых значений.

Необязательно обнулять. Достаточно чтобы были какие-либо определенные значения. В вашем случае "0001".

И можжно ссылку на номера строк листинга где двойное присваивание?

30-я строка блока 4DFF и строки 56-59.

при этом схема не будет зависеть от количества триггеров (сейчас 4 потом хоть 10).

Почитайте, как пишутся сдвиговые регистры на VHDL, про тип std_logic_vector и про generic. Как уже намекали выше, ваш код можно сделать параметризируемым и сжать его до нескольких строк (без учета заголовков и объявлений).

Вот этого пока не описано. А стоило бы.

Необязательно обнулять. Достаточно чтобы были какие-либо определенные значения. В вашем случае "0001".

30-я строка блока 4DFF и строки 56-59.

Почитайте, как пишутся сдвиговые регистры на VHDL, про тип std_logic_vector и про generic. Как уже намекали выше, ваш код можно сделать параметризируемым и сжать его до нескольких строк (без учета заголовков и объявлений).

Необязательно обнулять. Достаточно чтобы были какие-либо определенные значения. В вашем случае "0001".

30-я строка блока 4DFF и строки 56-59.

Почитайте, как пишутся сдвиговые регистры на VHDL, про тип std_logic_vector и про generic. Как уже намекали выше, ваш код можно сделать параметризируемым и сжать его до нескольких строк (без учета заголовков и объявлений).

1. Для этого я пока ввёл промежуточный сигнал и 1 генерю им

2. Без обнулений были неопределённые значения

3. 56-59 - почему? это же просто сброс, он может потом раздельным быть, да и на не подключенные выводы ругается симулятор, до этого просто на земле сидел.

4. до generic я ещё не дошёл, мне бы простую схему запустить чтобы с ней разобраться

1. Для этого я пока ввёл промежуточный сигнал и 1 генерю им

2. Без обнулений были неопределённые значения

2. Без обнулений были неопределённые значения

Если все равно уже добавлен ресет, то можно устанавливать начальное значение по нему, без всяких промежуточных сигналов. Еще раз - дело не в обнулении, а в присвоении конкретных значений вместо дефолтных U, а нулевые они или нет - роли не играет.

Цитата

3. 56-59 - почему? это же просто сброс, он может потом раздельным быть, да и на не подключенные выводы ругается симулятор, до этого просто на земле сидел.

Не важно, что это в вашем или чьем-либо другом понимании, с точки зрения языка сигнал может иметь несколько драйверов только в одном процессе. Из приведенного описания получается, что Qi ВСЕГДА равен FFi, но при этом по любому изменению сигналов из списка чувствительности еще и оказывается равен нулю - так не бывает.

с точки зрения языка сигнал может иметь несколько драйверов только в одном процессе.

С точки зрения языка сигнал может иметь сколько угодно драйверов в сколько угодном количестве процессов. Результат определяется функцией разрешения (если для используемого типа она определена). Вот с точки зрения железа -- да, драйвер может быть только один.

Вообще я бы посоветовал автору делать сразу правильно. Всё Ваше устройство легко уместить в такой код:

Более того, при необходимости можно добавить параметры для настройки разрядности такого регистра и хоть 1000 разрядов делайте

Если цель состоит описать именно из отдельных триггеров (правда зачем ?) то можно:

1. Описать отдельно DFF с асинхронным сбросом :

2. И описать соединение триггеров между собой:

И опять же. В такое описание легко добавить параметры для задания разрядности регистра.

CODE

library ieee;

use ieee.std_logic_1164.all;

entity reg_aclr is

port

(

clk : in std_logic;

aclr : in std_logic;

D : in std_logic;

Q : out std_logic_vector(3 downto 0)

);

end entity;

architecture RTL of reg_aclr is

signal shreg: std_logic_vector(3 downto 0) := (others => '0');

begin

process(aclr, clk)

begin

if (aclr = '1') then

shreg <= (others => '0');

elsif (rising_edge(clk)) then

shreg <= shreg(2 downto 0) & (D or shreg(3));

end if;

end process;

Q <= shreg;

end architecture;

use ieee.std_logic_1164.all;

entity reg_aclr is

port

(

clk : in std_logic;

aclr : in std_logic;

D : in std_logic;

Q : out std_logic_vector(3 downto 0)

);

end entity;

architecture RTL of reg_aclr is

signal shreg: std_logic_vector(3 downto 0) := (others => '0');

begin

process(aclr, clk)

begin

if (aclr = '1') then

shreg <= (others => '0');

elsif (rising_edge(clk)) then

shreg <= shreg(2 downto 0) & (D or shreg(3));

end if;

end process;

Q <= shreg;

end architecture;

Более того, при необходимости можно добавить параметры для настройки разрядности такого регистра и хоть 1000 разрядов делайте

Если цель состоит описать именно из отдельных триггеров (правда зачем ?) то можно:

1. Описать отдельно DFF с асинхронным сбросом :

CODE

library ieee;

use ieee.std_logic_1164.all;

entity DFF_aclr is

port

(

clk : in std_logic;

aclr : in std_logic;

D : in std_logic;

Q : out std_logic := '0'

);

end entity;

architecture RTL of DFF_aclr is

begin

reg_proc : process(aclr, clk)

begin

if (aclr = '1') then

Q <= '0';

elsif (rising_edge(clk)) then

Q <= D;

end if;

end process;

end architecture;

use ieee.std_logic_1164.all;

entity DFF_aclr is

port

(

clk : in std_logic;

aclr : in std_logic;

D : in std_logic;

Q : out std_logic := '0'

);

end entity;

architecture RTL of DFF_aclr is

begin

reg_proc : process(aclr, clk)

begin

if (aclr = '1') then

Q <= '0';

elsif (rising_edge(clk)) then

Q <= D;

end if;

end process;

end architecture;

2. И описать соединение триггеров между собой:

CODE

library ieee;

use ieee.std_logic_1164.all;

entity reg_aclr is

port

(

clk : in std_logic;

aclr : in std_logic;

D : in std_logic;

Q : out std_logic_vector(3 downto 0)

);

end entity;

architecture RTL of reg_aclr is

signal iQ: std_logic_vector(3 downto 0) := (others => '0');

begin

--===============================================

-- Первый триггер в цепочке сдвигового регистра

--===============================================

DFF0_aclr_comp : entity work.DFF_aclr

port map

(

clk => clk,

aclr => aclr,

D => D or iq(3),

Q => iQ(0)

);

--===============================================

-- Остальные триггера

--===============================================

reg_3to1generate : for i in 0 to 2 generate

DFF_aclr_comp : entity work.DFF_aclr

port map

(

clk => clk,

aclr => aclr,

D => iQ(i),

Q => iQ(i + 1)

);

end generate;

Q <= iQ;

end architecture;

use ieee.std_logic_1164.all;

entity reg_aclr is

port

(

clk : in std_logic;

aclr : in std_logic;

D : in std_logic;

Q : out std_logic_vector(3 downto 0)

);

end entity;

architecture RTL of reg_aclr is

signal iQ: std_logic_vector(3 downto 0) := (others => '0');

begin

--===============================================

-- Первый триггер в цепочке сдвигового регистра

--===============================================

DFF0_aclr_comp : entity work.DFF_aclr

port map

(

clk => clk,

aclr => aclr,

D => D or iq(3),

Q => iQ(0)

);

--===============================================

-- Остальные триггера

--===============================================

reg_3to1generate : for i in 0 to 2 generate

DFF_aclr_comp : entity work.DFF_aclr

port map

(

clk => clk,

aclr => aclr,

D => iQ(i),

Q => iQ(i + 1)

);

end generate;

Q <= iQ;

end architecture;

И опять же. В такое описание легко добавить параметры для задания разрядности регистра.

Спасибо за помощь, воспользуюсь обязательно всеми советами, но сейчас хочется разобраться почему мой код не работает и как его запустить, чтобы понять где ошибка.

Код

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_signed.all;

use IEEE.std_logic_unsigned.all;

entity \3REG\ is

port(

CLKT : in STD_LOGIC;

RS : in STD_LOGIC;

RST : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR(0 to 3):= (others => '0')

);

end \3REG\;

architecture \3REG\ of \3REG\ is

component \4DFF\

port (

CLK : in STD_LOGIC;

D0,D1,D2,D3 : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC

);

end component;

signal D0 : STD_LOGIC;

signal QT0,QT1,QT2,QT3 : STD_LOGIC := '0';

begin

U10 : \4DFF\

port map(

CLK => CLKT,

D0 => D0,

D1 => QT0,

D2 => QT1,

D3 => QT2,

Q0 => QT0,

Q1 => QT1,

Q2 => QT2,

Q3 => QT3,

RS0 => RST,

RS1 => RST,

RS2 => RST,

RS3 => RST

);

Q(3) <= QT3;

Q(2) <= QT2;

Q(1) <= QT1;

Q(0) <= QT0;

D0 <= RS or QT3;

end \3REG\;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_signed.all;

use IEEE.std_logic_unsigned.all;

entity \3REG\ is

port(

CLKT : in STD_LOGIC;

RS : in STD_LOGIC;

RST : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR(0 to 3):= (others => '0')

);

end \3REG\;

architecture \3REG\ of \3REG\ is

component \4DFF\

port (

CLK : in STD_LOGIC;

D0,D1,D2,D3 : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC

);

end component;

signal D0 : STD_LOGIC;

signal QT0,QT1,QT2,QT3 : STD_LOGIC := '0';

begin

U10 : \4DFF\

port map(

CLK => CLKT,

D0 => D0,

D1 => QT0,

D2 => QT1,

D3 => QT2,

Q0 => QT0,

Q1 => QT1,

Q2 => QT2,

Q3 => QT3,

RS0 => RST,

RS1 => RST,

RS2 => RST,

RS3 => RST

);

Q(3) <= QT3;

Q(2) <= QT2;

Q(1) <= QT1;

Q(0) <= QT0;

D0 <= RS or QT3;

end \3REG\;

и исправленный тригер

Код

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity \4DFF\ is

port(

D0,D1,D2,D3 : in STD_LOGIC;

CLK : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC := '0'

);

end \4DFF\;

architecture \4DFF\ of \4DFF\ is

begin

process( CLK,RS0,RS1,RS2,RS3 )

begin

if ( RS0='1') then Q0 <= '0';

elsif ( rising_edge (CLK)) then Q0 <= D0;

end if;

if ( RS1='1') then Q1 <= '0';

elsif ( rising_edge (CLK)) then Q1 <= D1;

end if;

if ( RS2='1') then Q2 <= '0';

elsif ( rising_edge (CLK)) then Q2 <= D2;

end if;

if ( RS3='1') then Q3 <= '0';

elsif ( rising_edge (CLK) ) then Q3 <= D3;

end if;

end process;

end \4DFF\;

use IEEE.STD_LOGIC_1164.all;

entity \4DFF\ is

port(

D0,D1,D2,D3 : in STD_LOGIC;

CLK : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC := '0'

);

end \4DFF\;

architecture \4DFF\ of \4DFF\ is

begin

process( CLK,RS0,RS1,RS2,RS3 )

begin

if ( RS0='1') then Q0 <= '0';

elsif ( rising_edge (CLK)) then Q0 <= D0;

end if;

if ( RS1='1') then Q1 <= '0';

elsif ( rising_edge (CLK)) then Q1 <= D1;

end if;

if ( RS2='1') then Q2 <= '0';

elsif ( rising_edge (CLK)) then Q2 <= D2;

end if;

if ( RS3='1') then Q3 <= '0';

elsif ( rising_edge (CLK) ) then Q3 <= D3;

end if;

end process;

end \4DFF\;

Запустил на Modelsim

1. Пока не убрал слеши из названия модулей не работало.

Теперь файлы регистра выглядит так:

2. Убрал ненужные библиотеки. Зачем Вы их подключали я не знаю. Но в принципе они не влияли никак.

С таким тестбенчем все работает как и должно:

Вывод : я предполагаю, что некорректные имена вида \name\

1. Пока не убрал слеши из названия модулей не работало.

Теперь файлы регистра выглядит так:

CODE

library ieee;

use ieee.std_logic_1164.all;

entity DFF_aclr is

port

(

D0,D1,D2,D3 : in STD_LOGIC;

CLK : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC := '0'

);

end DFF_aclr;

architecture DFF_aclr of DFF_aclr is

begin

process

(

CLK,

RS0,

RS1,

RS2,

RS3

)

begin

if (RS0='1') then

Q0 <= '0';

elsif (rising_edge (CLK)) then

Q0 <= D0;

end if;

if (RS1='1') then

Q1 <= '0';

elsif (rising_edge (CLK)) then

Q1 <= D1;

end if;

if (RS2='1') then

Q2 <= '0';

elsif (rising_edge (CLK)) then

Q2 <= D2;

end if;

if (RS3='1') then

Q3 <= '0';

elsif (rising_edge (CLK)) then

Q3 <= D3;

end if;

end process;

end DFF_aclr;

use ieee.std_logic_1164.all;

entity DFF_aclr is

port

(

D0,D1,D2,D3 : in STD_LOGIC;

CLK : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC := '0'

);

end DFF_aclr;

architecture DFF_aclr of DFF_aclr is

begin

process

(

CLK,

RS0,

RS1,

RS2,

RS3

)

begin

if (RS0='1') then

Q0 <= '0';

elsif (rising_edge (CLK)) then

Q0 <= D0;

end if;

if (RS1='1') then

Q1 <= '0';

elsif (rising_edge (CLK)) then

Q1 <= D1;

end if;

if (RS2='1') then

Q2 <= '0';

elsif (rising_edge (CLK)) then

Q2 <= D2;

end if;

if (RS3='1') then

Q3 <= '0';

elsif (rising_edge (CLK)) then

Q3 <= D3;

end if;

end process;

end DFF_aclr;

2. Убрал ненужные библиотеки. Зачем Вы их подключали я не знаю. Но в принципе они не влияли никак.

CODE

library IEEE;

use IEEE.std_logic_1164.all;

entity reg_aclr is

port(

CLKT : in STD_LOGIC;

RS : in STD_LOGIC;

RST : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR(0 to 3):= (others => '0')

);

end reg_aclr;

architecture reg_aclr of reg_aclr is

component DFF_aclr

port (

CLK : in STD_LOGIC;

D0,D1,D2,D3 : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC

);

end component;

signal D0 : STD_LOGIC;

signal QT0,QT1,QT2,QT3 : STD_LOGIC := '0';

begin

U10 : DFF_aclr

port map(

CLK => CLKT,

D0 => D0,

D1 => QT0,

D2 => QT1,

D3 => QT2,

Q0 => QT0,

Q1 => QT1,

Q2 => QT2,

Q3 => QT3,

RS0 => RST,

RS1 => RST,

RS2 => RST,

RS3 => RST

);

Q(3) <= QT3;

Q(2) <= QT2;

Q(1) <= QT1;

Q(0) <= QT0;

D0 <= RS or QT3;

end reg_aclr;

use IEEE.std_logic_1164.all;

entity reg_aclr is

port(

CLKT : in STD_LOGIC;

RS : in STD_LOGIC;

RST : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR(0 to 3):= (others => '0')

);

end reg_aclr;

architecture reg_aclr of reg_aclr is

component DFF_aclr

port (

CLK : in STD_LOGIC;

D0,D1,D2,D3 : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC

);

end component;

signal D0 : STD_LOGIC;

signal QT0,QT1,QT2,QT3 : STD_LOGIC := '0';

begin

U10 : DFF_aclr

port map(

CLK => CLKT,

D0 => D0,

D1 => QT0,

D2 => QT1,

D3 => QT2,

Q0 => QT0,

Q1 => QT1,

Q2 => QT2,

Q3 => QT3,

RS0 => RST,

RS1 => RST,

RS2 => RST,

RS3 => RST

);

Q(3) <= QT3;

Q(2) <= QT2;

Q(1) <= QT1;

Q(0) <= QT0;

D0 <= RS or QT3;

end reg_aclr;

С таким тестбенчем все работает как и должно:

CODE

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY reg_aclr_vhd_tst IS

END reg_aclr_vhd_tst;

ARCHITECTURE reg_aclr_arch OF reg_aclr_vhd_tst IS

-- constants

-- signals

SIGNAL CLKT : STD_LOGIC;

SIGNAL Q : STD_LOGIC_VECTOR(0 TO 3);

SIGNAL RS : STD_LOGIC := '0';

SIGNAL RST : STD_LOGIC := '0';

COMPONENT reg_aclr

PORT (

CLKT : IN STD_LOGIC;

Q : OUT STD_LOGIC_VECTOR(0 TO 3);

RS : IN STD_LOGIC;

RST : IN STD_LOGIC

);

END COMPONENT;

--▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓

--========================================================================

-- Формирование констант для вычисления периодв CLK от частоты работы

--========================================================================

constant clk_freq : real := 100.0; -- MHz

constant clk_prd : time := (1000.0/clk_freq) * 1.0 ns; -- Вычисление периода CLK

BEGIN

i1 : reg_aclr

PORT MAP (

-- list connections between master ports and signals

CLKT => CLKT,

Q => Q,

RS => RS,

RST => RST

);

--==========================================

-- Задание тактовой частоты проекта

--==========================================

process

begin

CLKT <= '0'; wait for clk_prd/2;

CLKT <= '1'; wait for clk_prd/2;

end process;

process

begin

wait for 15*clk_prd;

RS <= '1';

wait for clk_prd;

RS <= '0';

wait;

end process;

process

begin

wait for 50*clk_prd;

RST <= '1';

wait for 3*clk_prd;

RST <= '0';

wait;

end process;

END reg_aclr_arch;

USE ieee.std_logic_1164.all;

ENTITY reg_aclr_vhd_tst IS

END reg_aclr_vhd_tst;

ARCHITECTURE reg_aclr_arch OF reg_aclr_vhd_tst IS

-- constants

-- signals

SIGNAL CLKT : STD_LOGIC;

SIGNAL Q : STD_LOGIC_VECTOR(0 TO 3);

SIGNAL RS : STD_LOGIC := '0';

SIGNAL RST : STD_LOGIC := '0';

COMPONENT reg_aclr

PORT (

CLKT : IN STD_LOGIC;

Q : OUT STD_LOGIC_VECTOR(0 TO 3);

RS : IN STD_LOGIC;

RST : IN STD_LOGIC

);

END COMPONENT;

--▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓▓

--========================================================================

-- Формирование констант для вычисления периодв CLK от частоты работы

--========================================================================

constant clk_freq : real := 100.0; -- MHz

constant clk_prd : time := (1000.0/clk_freq) * 1.0 ns; -- Вычисление периода CLK

BEGIN

i1 : reg_aclr

PORT MAP (

-- list connections between master ports and signals

CLKT => CLKT,

Q => Q,

RS => RS,

RST => RST

);

--==========================================

-- Задание тактовой частоты проекта

--==========================================

process

begin

CLKT <= '0'; wait for clk_prd/2;

CLKT <= '1'; wait for clk_prd/2;

end process;

process

begin

wait for 15*clk_prd;

RS <= '1';

wait for clk_prd;

RS <= '0';

wait;

end process;

process

begin

wait for 50*clk_prd;

RST <= '1';

wait for 3*clk_prd;

RST <= '0';

wait;

end process;

END reg_aclr_arch;

Вывод : я предполагаю, что некорректные имена вида \name\

А в чем проблема теперь? Подайте сброс, подайте ваш RS меньше чем на такт, на такт, два, четыре. Посмотрите, как именно у вас не работает. Подскажу, если подадите на один такт, работать будет, но, скорее всего, только один раз. А потом послушайте совета, сбрасывайте один из тригеров в '1' и используйте для перезапуска сигнал RST.

use IEEE.std_logic_arith.all;

use IEEE.std_logic_signed.all;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_signed.all;

use IEEE.std_logic_unsigned.all;

Во-первых, эти библиотеки вам не нужны, если вы не используете математические функции.

В-вторых, использование std_logic_signed и std_logic_unsigned в одном модуле несколько странно.

В-третьих, не используйте их вообще. Используйте стандартную библиотеку numeric_std

Пока не убрал слеши из названия модулей не работало.

Там имя архитектуры совпадает с именем модуля. Почему-то.

Всю жизнь думал, что имена entity и связанного с ним архитектурного тела должны быть разными.

Ну и ладно.

Ну и ладно.

У вас же раньше все моделировалось. Иксы были, почти там, где надо. Там, где не надо, вероятно, вызывались рукописной задержкой присвоения на 1 ns. Покажите, что получается сейчас.

С именами \name\ всё нормально. Это расширенные идентификаторы, появившиеся в VHDL'93.

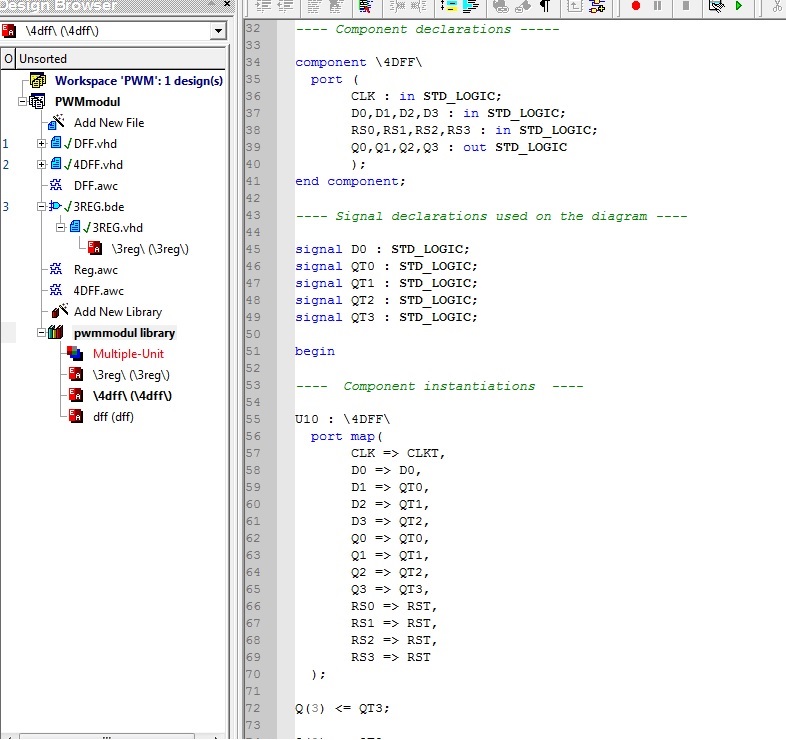

Переписал проект

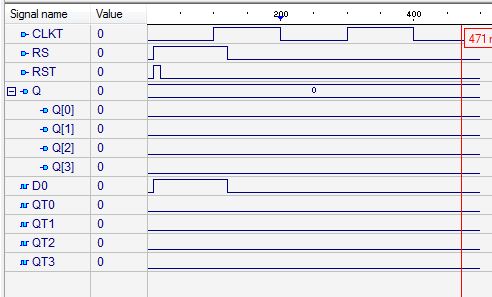

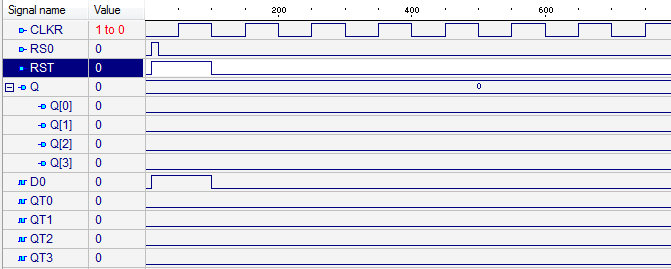

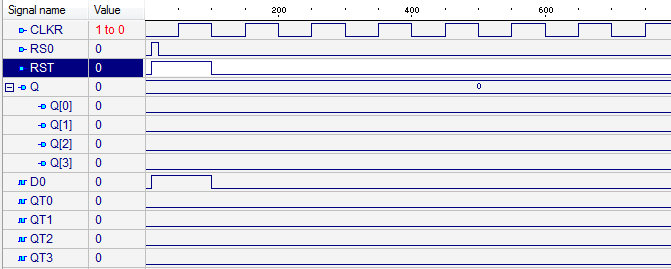

Тестбенч генерил методами синтезатора, не знаю как текст такой ввести, вот результат - тот же самый, тригеры не переключаются.

На совпадение имён не обращайте внимания, заметил, поправил, ничего не изменилось

Код

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity REG30 is

port(

CLKR : in STD_LOGIC;

RS0 : in STD_LOGIC;

RST : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR(0 to 3) := (others => '0')

);

end REG30;

architecture RTL of REG30 is

component DFF4

port (

CLK : in STD_LOGIC;

D0,D1,D2,D3 : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC

);

end component;

signal D0 : STD_LOGIC;

signal QT0,QT1,QT2,QT3 : STD_LOGIC := '0';

begin

U1 : DFF4

port map(

CLK => CLKR,

D0 => D0,

D1 => QT0,

D2 => QT1,

D3 => QT2,

Q0 => QT0,

Q1 => QT1,

Q2 => QT2,

Q3 => QT3,

RS0 => RS0,

RS1 => RS0,

RS2 => RS0,

RS3 => RS0

);

Q(3) <= QT3;

Q(2) <= QT2;

Q(1) <= QT1;

Q(0) <= QT0;

D0 <= RST or QT3;

end architecture;

use IEEE.STD_LOGIC_1164.all;

entity REG30 is

port(

CLKR : in STD_LOGIC;

RS0 : in STD_LOGIC;

RST : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR(0 to 3) := (others => '0')

);

end REG30;

architecture RTL of REG30 is

component DFF4

port (

CLK : in STD_LOGIC;

D0,D1,D2,D3 : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC

);

end component;

signal D0 : STD_LOGIC;

signal QT0,QT1,QT2,QT3 : STD_LOGIC := '0';

begin

U1 : DFF4

port map(

CLK => CLKR,

D0 => D0,

D1 => QT0,

D2 => QT1,

D3 => QT2,

Q0 => QT0,

Q1 => QT1,

Q2 => QT2,

Q3 => QT3,

RS0 => RS0,

RS1 => RS0,

RS2 => RS0,

RS3 => RS0

);

Q(3) <= QT3;

Q(2) <= QT2;

Q(1) <= QT1;

Q(0) <= QT0;

D0 <= RST or QT3;

end architecture;

Тестбенч генерил методами синтезатора, не знаю как текст такой ввести, вот результат - тот же самый, тригеры не переключаются.

На совпадение имён не обращайте внимания, заметил, поправил, ничего не изменилось

У меня ваш код промоделировался так, как должен. Посмотрите внутрь блока DFF4. Может у вас по какой-то причине сигналы в него не заходят.

У меня ваш код промоделировался так, как должен. Посмотрите внутрь блока DFF4. Может у вас по какой-то причине сигналы в него не заходят.

Хорошо, а я не вижу где в этом десятке строк кода теряется сигнал.

Код

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity DFF4 is

port(

D0,D1,D2,D3 : in STD_LOGIC;

CLK : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC := '0'

);

end DFF4;

architecture RTL of DFF4 is

begin

process( CLK,RS0,RS1,RS2,RS3 )

begin

if ( RS0='1') then Q0 <= '0';

elsif ( rising_edge (CLK)) then Q0 <= D0;

end if;

if ( RS1='1') then Q1 <= '0';

elsif ( rising_edge (CLK)) then Q1 <= D1;

end if;

if ( RS2='1') then Q2 <= '0';

elsif ( rising_edge (CLK)) then Q2 <= D2;

end if;

if ( RS3='1') then Q3 <= '0';

elsif ( rising_edge (CLK) ) then Q3 <= D3;

end if;

end process;

end architecture;

use IEEE.STD_LOGIC_1164.all;

entity DFF4 is

port(

D0,D1,D2,D3 : in STD_LOGIC;

CLK : in STD_LOGIC;

RS0,RS1,RS2,RS3 : in STD_LOGIC;

Q0,Q1,Q2,Q3 : out STD_LOGIC := '0'

);

end DFF4;

architecture RTL of DFF4 is

begin

process( CLK,RS0,RS1,RS2,RS3 )

begin

if ( RS0='1') then Q0 <= '0';

elsif ( rising_edge (CLK)) then Q0 <= D0;

end if;

if ( RS1='1') then Q1 <= '0';

elsif ( rising_edge (CLK)) then Q1 <= D1;

end if;

if ( RS2='1') then Q2 <= '0';

elsif ( rising_edge (CLK)) then Q2 <= D2;

end if;

if ( RS3='1') then Q3 <= '0';

elsif ( rising_edge (CLK) ) then Q3 <= D3;

end if;

end process;

end architecture;

Вытащите эти сигналы и порты на временную диаграмму. Там видно будет. Код пока можно считать нормальным.

В Альдеке можно выводить не только сигналы верхнего уровня, но и любого уровня иерархии. Обычно иерархическое дерево после запуска моделирования находится слева от временной диаграммы на месте списка файлов. В вашем случае интересно, что происходит внутри модуля U1. Ткните в него и вытащите все внутренние сигналы.

Для просмотра полной версии этой страницы, пожалуйста, пройдите по ссылке.