Полная версия этой страницы: DDR3: Терминация сигналов CK

Благодарю- а если TL c 65 ОМ поменять на 50(плюс минус 3 Ом)?

Не подключилась ваша модель.

У меня вышло вроде бы вложиться - Slow 868mV, Fast - 705mV.

В проекте

OBUFDS_inst : OBUFDS

generic map (

IOSTANDARD => "DIFF_SSTL15",

SLEW => "FAST")

port map (

O => DDR_CLK_p,

OB => DDR_CLK_n,

I => clk_in

);

В Implemented Design экспортировал, указав Updated generic IBIS and Updated parasitics package. Хотя модели 2013 года. Ну и Вивадо у меня 2015.4, тот который с Артиксом ставился.

С кондером Ccomp - Fast 840mV, Slow на том же уровне.

Signal - DDR_CLK

У меня вышло вроде бы вложиться - Slow 868mV, Fast - 705mV.

В проекте

OBUFDS_inst : OBUFDS

generic map (

IOSTANDARD => "DIFF_SSTL15",

SLEW => "FAST")

port map (

O => DDR_CLK_p,

OB => DDR_CLK_n,

I => clk_in

);

В Implemented Design экспортировал, указав Updated generic IBIS and Updated parasitics package. Хотя модели 2013 года. Ну и Вивадо у меня 2015.4, тот который с Артиксом ставился.

С кондером Ccomp - Fast 840mV, Slow на том же уровне.

Signal - DDR_CLK

Параметры модели отличаются, хотя и название одно и тоже.

Вот результаты с вашей и с той моделью что дали мне.Нажмите для просмотра прикрепленного файла

Вот что.

С 50 Ом трассой, и терминацией 50 Ом + Джиттер.

Нажмите для просмотра прикрепленного файла

С 40 Ом трассой, и терминацией 40 Ом + Джиттер.

Нажмите для просмотра прикрепленного файла

С 40 Ом трассой, и терминацией 40 Ом + Сcomp 3 pF + Джиттер.

Нажмите для просмотра прикрепленного файла

С 50 Ом трассой, и терминацией 50 Ом + Джиттер.

Нажмите для просмотра прикрепленного файла

С 40 Ом трассой, и терминацией 40 Ом + Джиттер.

Нажмите для просмотра прикрепленного файла

С 40 Ом трассой, и терминацией 40 Ом + Сcomp 3 pF + Джиттер.

Нажмите для просмотра прикрепленного файла

Цитата

Вот результаты с вашей и с той моделью что дали мне.

Для большей читаемости можно показать то же самое, но не используя один и тот же цвет для разных результатов?

Цитата

Вот что.

Здесь конечно сразу будут вопросы о том как вы задали джиттер(как мне помнится в гиперлинксе их несколько типов с настройкой магнитуды и пр), но вы можете показать весь сигнал? Не буду скрывать, хочу в том числе посмотреть что будет с искажением

Вы показываете total jitter, но это все можно увидеть и при "полном" сигнале- не нужно обрезать картинку, т.е покажите так чтобы был виден marginal jitter и Vpeak-peak. И к слову, откуда взялся в модели Ccomp, причем в таком размещении как у вас?

Volkov, спасибо за участие.

1. Две микросхемы памяти имеют независимые шины адреса намеренно. Обе микросхемы в связке работать не должны. В плате реализовано резервирование памяти.

2. Не понимаю, почему у вас модель не подключилась. Какая ошибка?

Напоминаю, что проблема с величиной Vix только в режиме Fast. Ниже привожу рисунки для режима typical:

Нажмите для просмотра прикрепленного файла

Интересно, как вам удалось (пост 48) улучшить результат почти на 40% (162 мВ против 263 мВ в посте 6).

1. Две микросхемы памяти имеют независимые шины адреса намеренно. Обе микросхемы в связке работать не должны. В плате реализовано резервирование памяти.

2. Не понимаю, почему у вас модель не подключилась. Какая ошибка?

Напоминаю, что проблема с величиной Vix только в режиме Fast. Ниже привожу рисунки для режима typical:

Нажмите для просмотра прикрепленного файла

Интересно, как вам удалось (пост 48) улучшить результат почти на 40% (162 мВ против 263 мВ в посте 6).

Интересно, как вам удалось (пост 48) улучшить результат почти на 40% (162 мВ против 263 мВ в посте 6).

Не знаю. Похоже ваша модель - это SSTL15_F_HR. А в моей DIFF_SSTL15_F_HR.

С джиттером долго разбираться, но похоже 1 UI слишком оптимистично. На выходе MMCM будет минимум 75 ps - 3%/.

По поводу конденсатора - то в JEDEC референсах он стоит на планках возле разъема. В Memory Down - нет требований по длине перед ним, но есть минимум Main Route + Neck-Down 500 mil после него.

чем длиннее трасса перед ним - тем сильнее он валит фронт.

Нажмите для просмотра прикрепленного файла

Volkov, по-моему я понял, почему у вас не заработала модель: я не скопировал в неё строки с описанием дифф. линий:

[Diff Pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

|

AM26 AN26 100mV 0 0 0

| C0_DDR3_dqs_p[1] DIFF_SSTL15_F_HR_IN50_P SSTL15_F_HR_IN50

AN34 AP34 100mV 0 0 0

| C0_DDR3_ck_p[0] DIFF_SSTL15_F_HR_P SSTL15_F_HR

AP29 AP30 100mV 0 0 0

| C0_DDR3_dqs_p[0] DIFF_SSTL15_F_HR_IN50_P SSTL15_F_HR_IN50

Теперь наши модели совпадают?

[Diff Pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

|

AM26 AN26 100mV 0 0 0

| C0_DDR3_dqs_p[1] DIFF_SSTL15_F_HR_IN50_P SSTL15_F_HR_IN50

AN34 AP34 100mV 0 0 0

| C0_DDR3_ck_p[0] DIFF_SSTL15_F_HR_P SSTL15_F_HR

AP29 AP30 100mV 0 0 0

| C0_DDR3_dqs_p[0] DIFF_SSTL15_F_HR_IN50_P SSTL15_F_HR_IN50

Теперь наши модели совпадают?

Цитата

По поводу конденсатора - то в JEDEC референсах он стоит на планках возле разъема.

Мне это известно

Такие же вопросы и про TL 65 и 40 Ом соответственно(откуда они взялись)- на вашей последней картинке звон виден отчетливо

Не знаю. Похоже ваша модель - это SSTL15_F_HR. А в моей DIFF_SSTL15_F_HR.

В вашем файле модели нет секции

[Package Model]

соответственно и нет доп. паразитных параметров которые должны были прописаться из файла ffg1156_7a200t.pkg,

а они то как раз и проводят к сдвигу фронтов на 150ps и повышению точки пересечения на 22mV, и выходу за пределы допуска Vix.

Нажмите для просмотра прикрепленного файла

В прочем в файле ffg1156_7a200t.pkg написано

Код

The data in this model has been generated with the utmost care and is believed to be accurate, although accuracy cannot be guaranteed. This model has not been correlated with lab measurements. .

Т.е. насколько можно доверять этим данным и их учитывать непонятно.

Цитата

В вашем файле модели нет секции

[Package Model]

соответственно и нет доп. паразитных параметров которые должны были прописаться из файла ffg1156_7a200t.pkg

а они как раз и проводят к сдвигу фронтов на 150ps и повышению точки пересечения на 22mV, и выходу за пределы допуска Vix.

[Package Model]

соответственно и нет доп. паразитных параметров которые должны были прописаться из файла ffg1156_7a200t.pkg

а они как раз и проводят к сдвигу фронтов на 150ps и повышению точки пересечения на 22mV, и выходу за пределы допуска Vix.

Ну хоть кто-то это сказал наконец

Т.е. раз за разом тема возвращается к кривости сетапа

Цитата

Т.е. насколько можно доверять этим данным и их учитывать непонятно.

А больше и неоткуда взять эти данные

Еще пару слов за сетап: представляется мягко говоря логичным прогнать сначала модель при идеальном интерконнекте, вестимо чтобы оценить не только ее корректность, но и работоспособность как таковую- на том же форуме хилых есть темы от людей у которых модели не взлетели. Далее, как только понятно что все ок, уже можно искать "пределы работоспособности", уродовать связи, играть с таймингами и пр.- тут же столько возни, а все напрасно, потому как с самого начала все сделано через задницу

Да, действитель не добавились.

Но тут, похоже, не только паразиты.

Если менять длину линии, то можно видеть максимумы и минимумы VIX.

При 1.6 - 930мВ, при 2.05 - 878мВ

Нажмите для просмотра прикрепленного файла

Похоже, что на драйвер влияет отраженный сигнал. Насколько это точно просчитывается, и можно ли таким образом подогнать длину линии, вот это интересно.

Но тут, похоже, не только паразиты.

Если менять длину линии, то можно видеть максимумы и минимумы VIX.

При 1.6 - 930мВ, при 2.05 - 878мВ

Нажмите для просмотра прикрепленного файла

Похоже, что на драйвер влияет отраженный сигнал. Насколько это точно просчитывается, и можно ли таким образом подогнать длину линии, вот это интересно.

Максимумы и минимумы так и должны быть, главное чтобы все укладывалось в рамки

Другая модель.

Длина основного сегмента - 2.9 in.

Нажмите для просмотра прикрепленного файла

Длина основного сегмента - 3.1 in.

Нажмите для просмотра прикрепленного файла

Длина основного сегмента - 2.9 in.

Нажмите для просмотра прикрепленного файла

Длина основного сегмента - 3.1 in.

Нажмите для просмотра прикрепленного файла

Volkov, попробовал две различные длины основного участка: исходную 1.55 дюйма и увеличенную до 10 дюймов. Точка пересечения приблизилась к идеалу на 41 мВ:

Нажмите для просмотра прикрепленного файла

Времена:

Исходная 1.55 дюйма:

Avg fall time: 120.780 ps Min fall time: 120.780 ps High voltage: 1.15 V

Max fall time: 120.780 ps Low voltage: 318.4 mV

Avg rise time: 100.318 ps Min rise time: 100.318 ps Low voltage: 389.2 mV

Max rise time: 100.318 ps High voltage: 1.17 V

Увеличенная до 10 дюймов:

Avg fall time: 90.678 ps Min fall time: 90.678 ps High voltage: 1.24 V

Max fall time: 90.678 ps Low voltage: 760.5 mV

Avg rise time: 92.021 ps Min rise time: 92.021 ps Low voltage: 330.9 mV

Max rise time: 92.021 ps High voltage: 868.5 mV

Нажмите для просмотра прикрепленного файла

Времена:

Исходная 1.55 дюйма:

Avg fall time: 120.780 ps Min fall time: 120.780 ps High voltage: 1.15 V

Max fall time: 120.780 ps Low voltage: 318.4 mV

Avg rise time: 100.318 ps Min rise time: 100.318 ps Low voltage: 389.2 mV

Max rise time: 100.318 ps High voltage: 1.17 V

Увеличенная до 10 дюймов:

Avg fall time: 90.678 ps Min fall time: 90.678 ps High voltage: 1.24 V

Max fall time: 90.678 ps Low voltage: 760.5 mV

Avg rise time: 92.021 ps Min rise time: 92.021 ps Low voltage: 330.9 mV

Max rise time: 92.021 ps High voltage: 868.5 mV

Цитата

Другая модель.

Модель линии покажите заодно- при таких искажениях ясно что как минимум импедансы TL заметно отличаются от того что заложено в контроллер

Цитата

попробовал две различные длины основного участка: исходную 1.55 дюйма и увеличенную до 10 дюймов.

Похоже, что на драйвер влияет отраженный сигнал. Насколько это точно просчитывается, и можно ли таким образом подогнать длину линии, вот это интересно.

Запускаете Sweep и смотрите. Например изменение длины от 2 до 20см с шагом 1см - Vix постепенно опускается на 29mV:

Нажмите для просмотра прикрепленного файла

Изменение импеданса линии естественно влияет на форму сигнала, но не на точку Vix.

Нажмите для просмотра прикрепленного файла

40 - желтый

50 - зеленый

60 - красный

ширина линии 100мкм, зазор 100мкм, длина 3см

Ну и изменение формы при изменении длины

Нажмите для просмотра прикрепленного файла

2-8-14-20см

зеленый-красный-желтый-голубой

Нажмите для просмотра прикрепленного файла

2-4-6-8-10см

Т.е. при 8см имеем практически идеальный сигнал.

"Идеально"- это как на вашей прошлой картинке? Лучше чем 50 и 50?

Это как на картинке слева - намного лучше.

А вот справа - трасса на 0.4 дюйма длиннее. При тех же импедансах - 40 /60.

Нажмите для просмотра прикрепленного файла

Цитата

Это как на картинке слева - намного лучше.

Меня конечно веселят ваши уходы от прямого ответа

Меня конечно веселят ваши уходы от прямого ответа  (в частности от вопроса касаемо происхождения TL в 40 и 60 Ом), однако тут нельзя не отметить что эта картинка слева идеалом ни разу не является

(в частности от вопроса касаемо происхождения TL в 40 и 60 Ом), однако тут нельзя не отметить что эта картинка слева идеалом ни разу не является

А почему бы вам не ответить, на свой же вопрос. Где будет более открытый eye, а где наименее, если 50/50 ? И почему так будет происходить. Вы же как бы это знаете, так просветили бы.

идеалом ни разу не является

Меня устраивает, даже длину с меньшим резонансом подогнал. Если это резонанс, хотя что же, если не оно.

Цитата

А почему бы вам не ответить, на свой же вопрос.

Вы знаете, читая строчки вроде этой:

Цитата

Меня устраивает, даже длину с меньшим резонансом подогнал. Если это резонанс, хотя что же, если не оно.

а также припоминая ваши ответы из других тем, должен таки согласиться с вами в том, что ответ на свой собственный вопрос мне самому все же известен и вполне себе давно

Цитата

так просветили бы.

Просветительской деятельностью к сожалению не занимаюсь, для меня электроникс является по большей части смесью пикабу с уродру- уж такие темы с таким контентом и подавно

Volkov или другие специалисты, вы не подскажете с учётом влияний паразитностей корпуса на задержку?

Необходимо получить данные по задержкам внутри корпуса. Для ПЛИС (xc7a200tffg1156-2) всё просто: есть данные, выгруженные из Vivado. Например, для AL34, задержка составляет от 164,101 до 165,751 пс. Проверяем по IBIS (берём данные из Inductance и Capacitance Matrix): корень(7,22116е-11*3,76679е-12) = 164,92 пс.

Для памяти MT41J128M16JT есть как Inductance и Capacitance Matrix, так и значения в начале модели, причём эти данные не совпадают. Например, для вывода A1 индуктивность в начале указана 1,755 нГн, а в разделе Inductance Matrix 2,28 нГн. Какое значение брать?

Спасибо.

Необходимо получить данные по задержкам внутри корпуса. Для ПЛИС (xc7a200tffg1156-2) всё просто: есть данные, выгруженные из Vivado. Например, для AL34, задержка составляет от 164,101 до 165,751 пс. Проверяем по IBIS (берём данные из Inductance и Capacitance Matrix): корень(7,22116е-11*3,76679е-12) = 164,92 пс.

Для памяти MT41J128M16JT есть как Inductance и Capacitance Matrix, так и значения в начале модели, причём эти данные не совпадают. Например, для вывода A1 индуктивность в начале указана 1,755 нГн, а в разделе Inductance Matrix 2,28 нГн. Какое значение брать?

Спасибо.

Изучите JEDEC STANDARD для вашей DDR3L SDRAM, поскольку она соответствует своему стандарту. Задержки там все приведены к "нулю" внутри микросхемы. Можете убедиться, перевернув и посмотрев вашу DDR3L SDRAM под микроскопом, ту многослойку с BGA шариками. Там видны меандры, трамбоны до нужных площадок, шаров BGA. Зачем вам что-то еще брать? Будет другой производитель DDR3L с другими параметрами, но все допуски и разбросы "нуля"оговорены. Думаю вам нужно заниматься другой стороной, вашей ПЛИС, задержкой внутри корпуса и трассой до вашей памяти только. Тем более что скорости у вас "никакие", допуски "огромные".

И еще поймите, что внутри всех DDR2/3/4/5 находится сложный умный логический автомат по подстройки сотни параметров по частотам, времянкам, уровням. Который сильно облегчает жизнь всем вашим точным подгонкам.

И еще поймите, что внутри всех DDR2/3/4/5 находится сложный умный логический автомат по подстройки сотни параметров по частотам, времянкам, уровням. Который сильно облегчает жизнь всем вашим точным подгонкам.

Aner, спасибо. То есть правило такое: выравниваем трассы только с учётом задержек внутри ПЛИС, а задержки внутри корпуса памяти не учитываем, т. к. они скомпенсированы производителем?

Ещё вопрос в тему: при разводке PCI Express x4 gen. 2 также нужно учитывать задержки внутри корпуса ПЛИС (Artix-7), или они уже скомпенсированы производителем?

Ещё вопрос в тему: при разводке PCI Express x4 gen. 2 также нужно учитывать задержки внутри корпуса ПЛИС (Artix-7), или они уже скомпенсированы производителем?

Aner, спасибо. То есть правило такое: выравниваем трассы только с учётом задержек внутри ПЛИС, а задержки внутри корпуса памяти не учитываем, т. к. они скомпенсированы производителем?

Ещё вопрос в тему: при разводке PCI Express x4 gen. 2 также нужно учитывать задержки внутри корпуса ПЛИС (Artix-7), или они уже скомпенсированы производителем?

Ещё вопрос в тему: при разводке PCI Express x4 gen. 2 также нужно учитывать задержки внутри корпуса ПЛИС (Artix-7), или они уже скомпенсированы производителем?

Еще раз изучайте стандарты того что применяете, на подсказках далеко не уедете! ... задержки внутри корпуса памяти не учитываем, т. к. они скомпенсированы и соответствуют стандартам!

Задержки внутри корпуса ПЛИС не могут быть скомпенсированы которые даны пользователю для использование в различных проектах, разных конфигурациях; IP блоки их реализации могут быть исключением, также аппаратный интерфейс DDR, но это все описано и даны подробности в AN.

Думаю для PCI Express x4 gen. 2 нужно учитывать задержки внутри корпуса ПЛИС (Artix-7) если в выбранной вами реализации IP Core не поддержана реализация автомата компенсации.

У Xilinx даже аппаратный контроллер в Zynq требует учёта задержек внутри корпуса; вот тема с их форума.

По PCIe напишу здесь, когда выясню.

По PCIe напишу здесь, когда выясню.

По ПЛИС (Artix-7)

Это понятно?

...

I/O Logic

Input and Output Delay. All inputs and outputs can be configured as either combinatoria l or registered. Double data rate (DDR) is supported by all

inputs and outputs. Any input and some outputs can be individually delayed by up to 32 increments of 78 ps, 52 ps, or 39 ps each. Such delays are implemented as IDELAY and ODELAY. The number of delay steps can be set by configuration and can also be incremented or decremented while in use.

Вы определитесь, вам Цинки или Артиксы или хз? Тамже разные технологии, все другое хотя внешне похоже, Цинки ближе с SoC_ам.

Это понятно?

...

I/O Logic

Input and Output Delay. All inputs and outputs can be configured as either combinatoria l or registered. Double data rate (DDR) is supported by all

inputs and outputs. Any input and some outputs can be individually delayed by up to 32 increments of 78 ps, 52 ps, or 39 ps each. Such delays are implemented as IDELAY and ODELAY. The number of delay steps can be set by configuration and can also be incremented or decremented while in use.

Вы определитесь, вам Цинки или Артиксы или хз? Тамже разные технологии, все другое хотя внешне похоже, Цинки ближе с SoC_ам.

Aner, понятно. Сейчас говорим про Артикс.

Наверное, поэтому для Артикса рекомендуется задерживать такт относительно строба на 150 пс и более (при допустимой задержке от 0 пс) - так проще выбрать задержку с фиксированными дискретами.

Наверное, поэтому для Артикса рекомендуется задерживать такт относительно строба на 150 пс и более (при допустимой задержке от 0 пс) - так проще выбрать задержку с фиксированными дискретами.

Там же вот ответ по Цинку: ... open a synthesized design ...

...The easiest way to export the pin flight time information is to open a synthesized design and in either the IO Ports or Package Pins view right click in the area, select "Export I/O Ports", select CSV, and then press OK. When you open the CSV file you'll see the PS memory interface pins in the "Site Type" column starting with "PS_".

Непонял, вы что только плату разводите? А сам проект на Артиксе кто-то другой делает?

...The easiest way to export the pin flight time information is to open a synthesized design and in either the IO Ports or Package Pins view right click in the area, select "Export I/O Ports", select CSV, and then press OK. When you open the CSV file you'll see the PS memory interface pins in the "Site Type" column starting with "PS_".

Aner, понятно. Сейчас говорим про Артикс.

Наверное, поэтому для Артикса рекомендуется задерживать такт относительно строба на 150 пс и более (при допустимой задержке от 0 пс) - так проще выбрать задержку с фиксированными дискретами.

Наверное, поэтому для Артикса рекомендуется задерживать такт относительно строба на 150 пс и более (при допустимой задержке от 0 пс) - так проще выбрать задержку с фиксированными дискретами.

Непонял, вы что только плату разводите? А сам проект на Артиксе кто-то другой делает?

Aner, уже сделал. Очень удобно.

Да, только схему и трассировку. Сборкой проекта занимаются коллеги. Причём столкнулся с необходимостью читать не только UG, но и PG (хотя зачем в PG включать информацию, нужную схемотехникам, так и не понял), из-за чего пришлось менять схему.

У вас есть мысли по основной проблеме с параметром Vix?

Да, только схему и трассировку. Сборкой проекта занимаются коллеги. Причём столкнулся с необходимостью читать не только UG, но и PG (хотя зачем в PG включать информацию, нужную схемотехникам, так и не понял), из-за чего пришлось менять схему.

У вас есть мысли по основной проблеме с параметром Vix?

Aner, уже сделал. Очень удобно.

У вас есть мысли по основной проблеме с параметром Vix?

У вас есть мысли по основной проблеме с параметром Vix?

На практике ассиметрии не встречал, наверное все по стандарту выполнял.

Вы делали реальные измерения или только симуляцией в гиперлинксе ограничились?

И что по вашему основная проблема?

Aner, несоответствие стандарту по уровню пересечения дифф. сигнала СК. Сейчас симуляция, разумеется.

Aner, несоответствие стандарту по уровню пересечения дифф. сигнала СК. Сейчас симуляция, разумеется.

Причин может быть много, разных и неожиданных. Больше походит на влияние окружения, плохой земли, ... может не на самой трассе а на питание LVDS драйверов. Если много слоев, пробуйте перенести в другой слой этот CK (обязательно между земляными) может будет зацепка и найдете влияние.

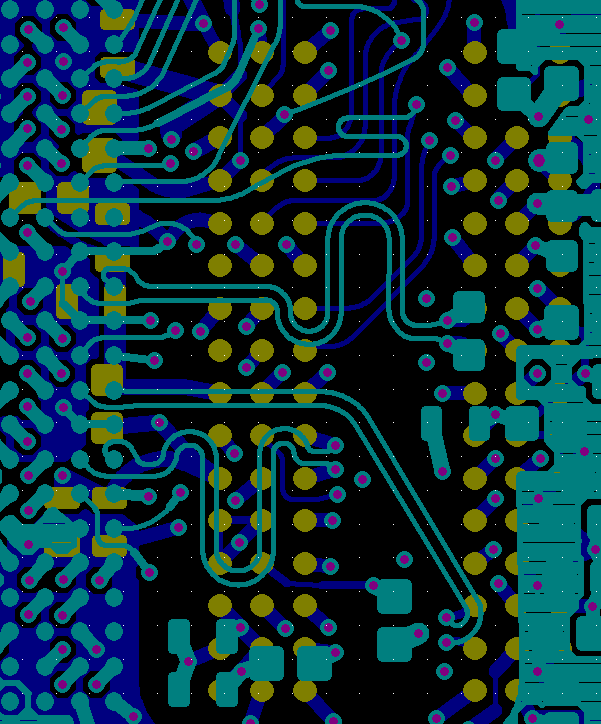

Еще пробуйте ваш меандры перевести в трамбоны, причем только на одной стороне линии, не так как сейчас на вашей каринке.

Мой пример для CK.

Цитата

нужно учитывать задержки внутри корпуса ПЛИС (Artix-7), или они уже скомпенсированы производителем?

Один и тот же кристалл ПЛИС обычно может упаковываться в несколько разных корпусов, поэтому для каждого корпуса задержки свои.

Товарищи, всем спасибо за ответы.

На форуме Xilinx ответили про PCI Express: данные задержек применять надо.

На форуме Xilinx ответили про PCI Express: данные задержек применять надо.

Внутри пары PCIE - да, надо учитывать, хотя они уже достаточно хорошо выравнены. А между парами выравнивание не нужно, потому как стандарт допускает разницу в 20ns(2.5GT/s), 8ns(5GT/s) или 6ns(8GT/s) между любыми линиями в пределах порта.

Для просмотра полной версии этой страницы, пожалуйста, пройдите по ссылке.