Полная версия этой страницы: Рекомендации по трассировке DDR3

На входах адресов встроенной терминации нет, поэтому как минимум не мешает проверить, как будет выглядеть сигнал. Пару часов назад посмотрел - неприятно удивился... без терминации выглядит отвратительно. Но это с моделями, которые были под рукой, целевые могут и по другому себя вести.

Цитата

-В руководстве есть фраза- CK and DQS trace lengths must be matched (±250 mil).... Я её понимаю так- СК и DQS должны иметь одинаковую длину с погрешностью 250мил(6.5мм). Учитывая что длина байтов у меня 32мм то и DQS у меня 32мм, и поэтому я и клок хотел уменьшать с 50 до 32мм

Перечитайте пост №44 и сравните еще раз с тем что пишут хилые.

Цитата

-Раз терминация в образце есть и на нём всё работает, то и я её решил оставить. Как по мне лучше предусмотреть место и если что, потом не запаивать.

Нет, безусловно внешней терминацией хуже не сделать

Цитата

Касательно того, что корпуса резисторов большие я уже понял и признал, каюсь. Просто как правило применяю 0603, и тут думал что нет необходимости мельчить. (Плюс читал статью на хабре что идентичный по номиналу и вольтажу кондер по характеристикам лучше в большем корпусе)

Это где вы такое прочитали? Что насчет вашего дизайна- на картинке хорошо видно что у вас уже заложены 0402 под спартаном, о чем разговор?

Цитата

-Биты я свапировал. И вроде раскрестил всё что мог.

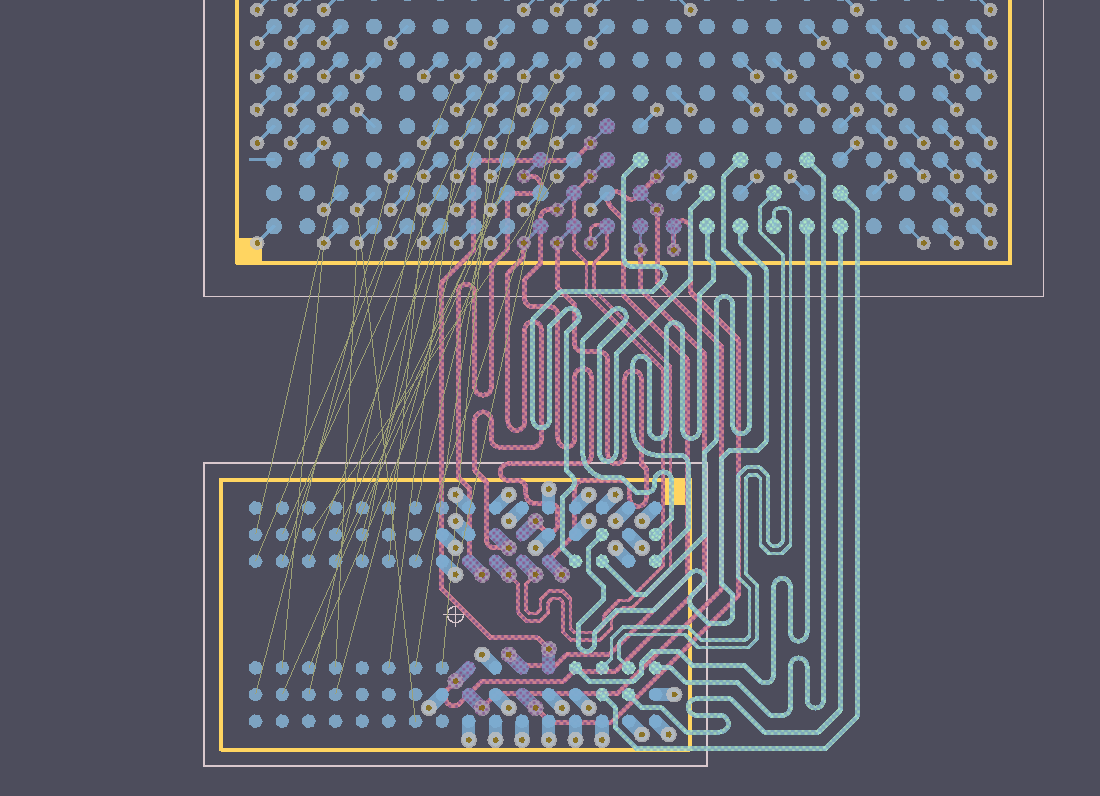

В чем смысл свапа- раскидать трассы настолько прямо чтобы разбег длин до таргета был минимальный. У вас же дичайшая накрутка, что намекает о кривизне сапа: трассы идут неоптимально. В контексте вашего вопроса про клок это вполне актуальный момент- решаете проблему которую сами себе и создали

Цитата

-Поясните пожалуйста эту фразу.

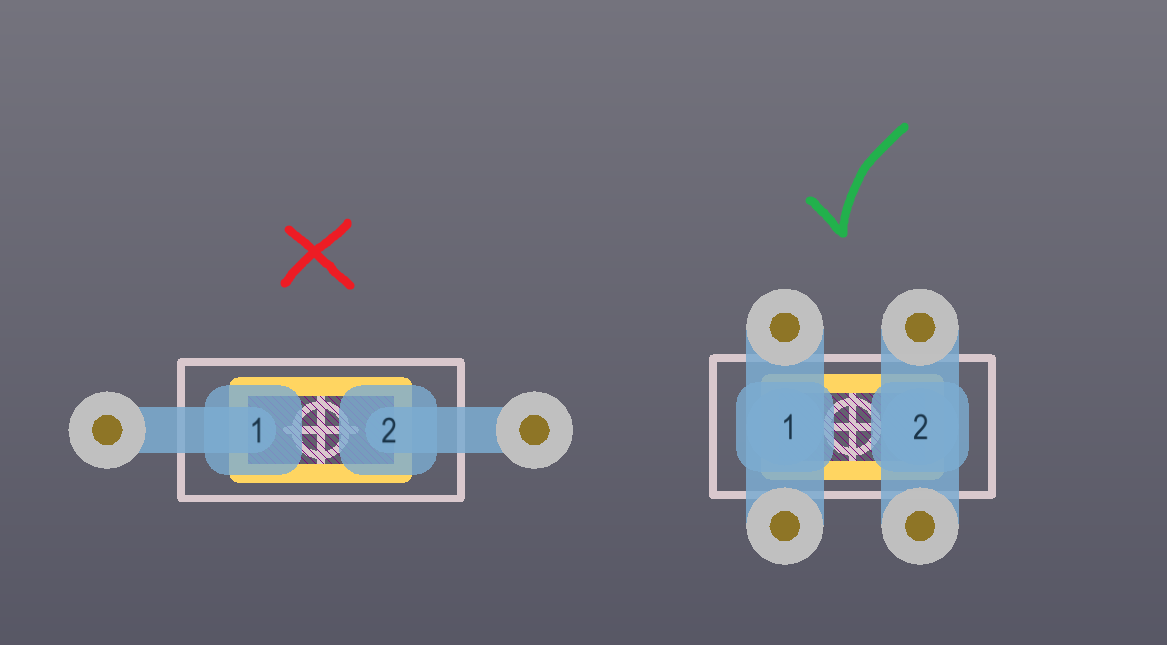

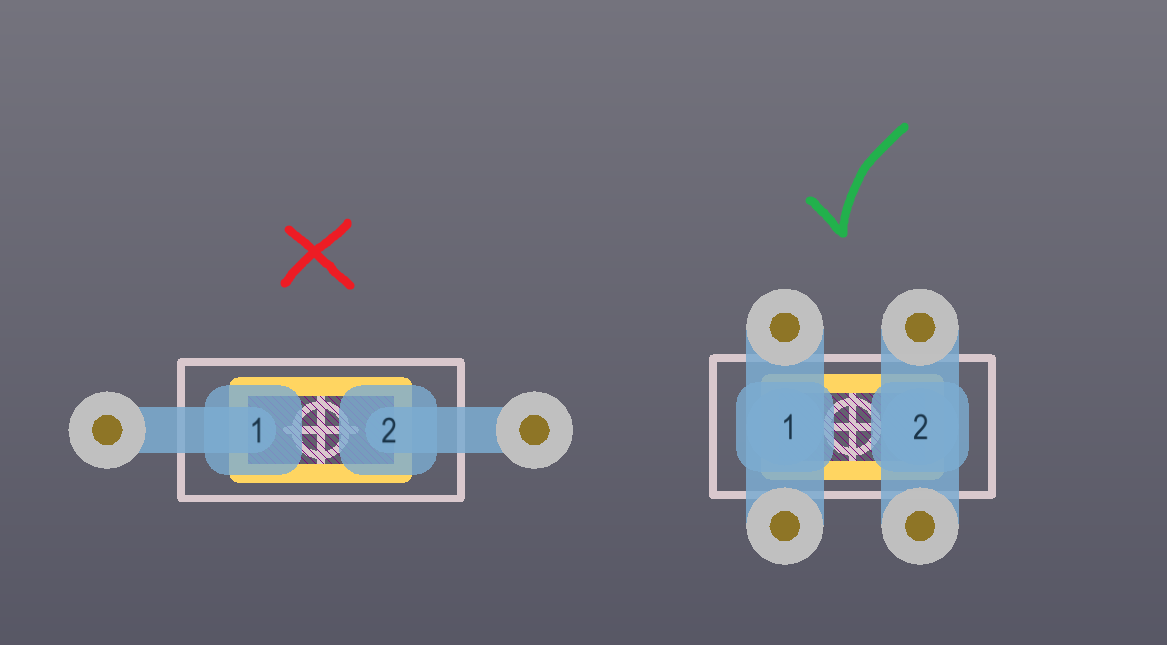

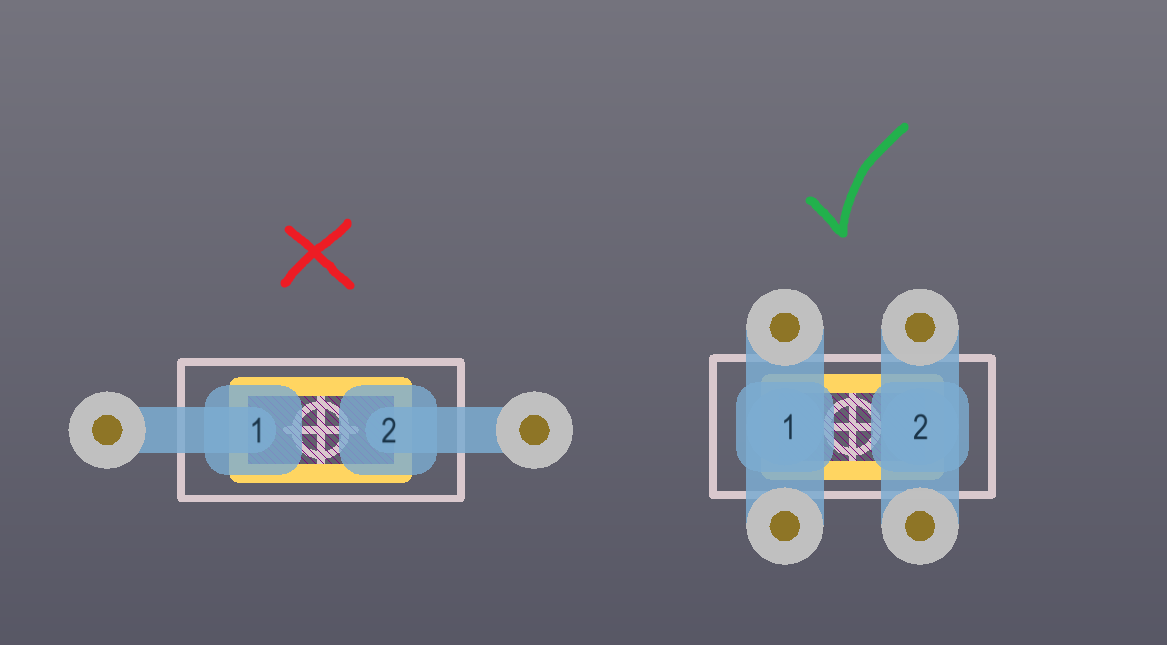

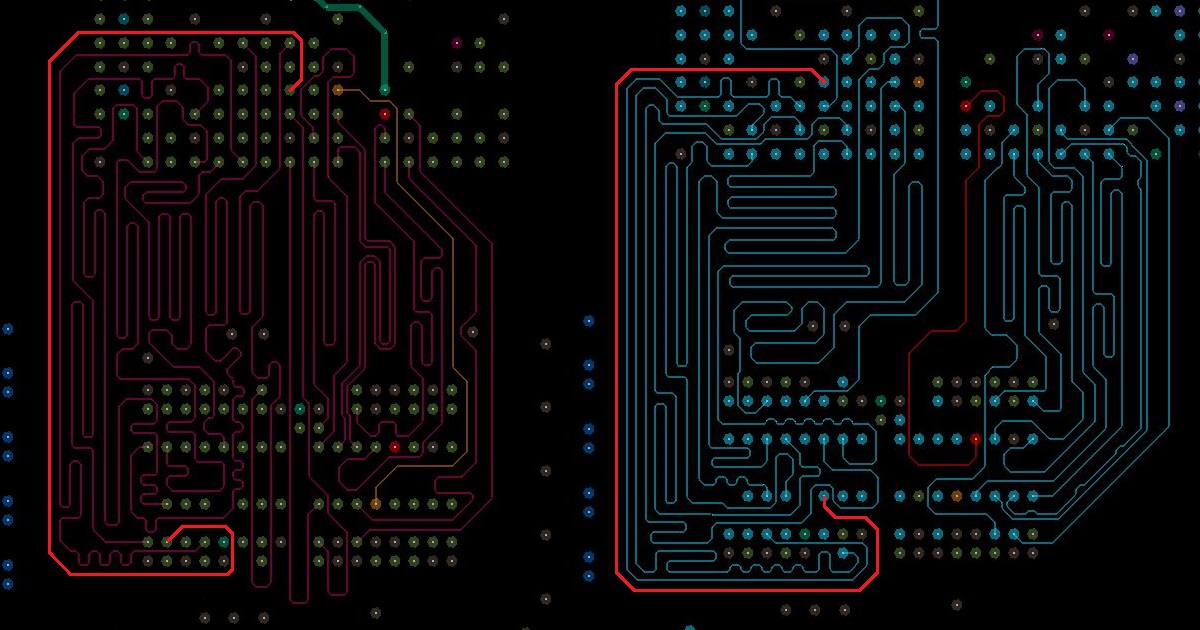

У вас сделано как на картинке слева, имеет смысл делать как справа

Цитата

По совпадению это как раз RST# ))

Цитата

На входах адресов встроенной терминации нет, поэтому как минимум не мешает проверить, как будет выглядеть сигнал. Пару часов назад посмотрел - неприятно удивился... без терминации выглядит отвратительно. Но это с моделями, которые были под рукой, целевые могут и по другому себя вести

Так в том и дело что все зависит от того на какой частоте работает память и какой длины вышли траски- для таких медленных скоростей как раз и нет проблем сделать так чтобы не было нужды во внешней терминации. Здесь в качестве попсового примера можно привести тот же BeagleBone Black.

Перечитайте пост №44 и сравните еще раз с тем что пишут хилые.

Нет, безусловно внешней терминацией хуже не сделать , но вот не запаивать ее нельзя- при ваших вводных у вас стабы будут космической длины. Хотя что-то мне подсказывает что спартан и такое переварит.

, но вот не запаивать ее нельзя- при ваших вводных у вас стабы будут космической длины. Хотя что-то мне подсказывает что спартан и такое переварит.

Это где вы такое прочитали? Что насчет вашего дизайна- на картинке хорошо видно что у вас уже заложены 0402 под спартаном, о чем разговор?

В чем смысл свапа- раскидать трассы настолько прямо чтобы разбег длин до таргета был минимальный. У вас же дичайшая накрутка, что намекает о кривизне сапа: трассы идут неоптимально. В контексте вашего вопроса про клок это вполне актуальный момент- решаете проблему которую сами себе и создали

У вас сделано как на картинке слева, имеет смысл делать как справа

Так в том и дело что все зависит от того на какой частоте работает память и какой длины вышли траски- для таких медленных скоростей как раз и нет проблем сделать так чтобы не было нужды во внешней терминации. Здесь в качестве попсового примера можно привести тот же BeagleBone Black.

Нет, безусловно внешней терминацией хуже не сделать

Это где вы такое прочитали? Что насчет вашего дизайна- на картинке хорошо видно что у вас уже заложены 0402 под спартаном, о чем разговор?

В чем смысл свапа- раскидать трассы настолько прямо чтобы разбег длин до таргета был минимальный. У вас же дичайшая накрутка, что намекает о кривизне сапа: трассы идут неоптимально. В контексте вашего вопроса про клок это вполне актуальный момент- решаете проблему которую сами себе и создали

У вас сделано как на картинке слева, имеет смысл делать как справа

Так в том и дело что все зависит от того на какой частоте работает память и какой длины вышли траски- для таких медленных скоростей как раз и нет проблем сделать так чтобы не было нужды во внешней терминации. Здесь в качестве попсового примера можно привести тот же BeagleBone Black.

-В посте 44 я отвечал Юрию, который писал что клоки как правило равны адресам. А адреса у меня 60мм, поэтому я спросил- наращивать до адресов-60мм или срезать до DQS -32мм.

К слову, я так и не понял какой длины сделать клок. Или "спартан всё схвает"?))

-Статья о кондёрах - https://geektimes.ru/post/263366/

- Под спартаном пришлось ставить 0402, тк 0603 что-то не влезали совсем)

А в чём смысл изменения подключения кондёров? Уменьшение индуктивности?

Цитата

-В посте 44 я отвечал Юрию, который писал что клоки как правило равны адресам. А адреса у меня 60мм, поэтому я спросил- наращивать до адресов-60мм или срезать до DQS -32мм.

К слову, я так и не понял какой длины сделать клок. Или "спартан всё схвает"?))

К слову, я так и не понял какой длины сделать клок. Или "спартан всё схвает"?))

Капитан очевидность намекает что нужно сделать как предлагают хилые, и попасть по длине CK vs DQS в промежуток 250милсов.

Цитата

-Статья о кондёрах - https://geektimes.ru/post/263366/

- Под спартаном пришлось ставить 0402, тк 0603 что-то не влезали совсем)

- Под спартаном пришлось ставить 0402, тк 0603 что-то не влезали совсем)

Вот оно что- ну тогда не мелочитесь, ставьте 1210 в ддр3, чтобы было прямо за-сь

Цитата

А в чём смысл изменения подключения кондёров? Уменьшение индуктивности?

Именно.

По поводу конденсаторов да, есть такой неприятный эффект. Но наиболее критично его проявление на выходах источников, хоть DCDC, хоть LDO(хотя для первого, конечно, важнее набрать нужную емкость). Но в случае декаплинга важнее малые размеры, чем определенная емкость. Так что даже не сомневайтесь - при прочих равных ставьте как можно меньшие корпуса.

хотел я картинку вставить по поводу спартана и ддр3, да куда то дел ее, не нашел. в общем, работало, лично видел на столе, с выравниванием меандром с зазорами 1w, так что на самом деле, делать зазоры меандра как у вас, оно конечно правильно, но не нужно. это несколько уплотнит дизайн. еще как то странно конденсаторы ддр3 стоят, мне глез режет, это имхо, я привых ставить суммарно 6шт вдол длинной стороны, соосно чипу. у микрона на эту тему аппликуха есть. и не забывайте, что спартан6, если мне память не изменяет, максимум что умеет, это всего ддр3-800, т.е.400МГц, а это частота, которая может прощать очень многое. В целом все ок, но просто необычно.

хотел я картинку вставить по поводу спартана и ддр3, да куда то дел ее, не нашел. в общем, работало, лично видел на столе, с выравниванием меандром с зазорами 1w, так что на самом деле, делать зазоры меандра как у вас, оно конечно правильно, но не нужно. это несколько уплотнит дизайн. еще как то странно конденсаторы ддр3 стоят, мне глез режет, это имхо, я привых ставить суммарно 6шт вдол длинной стороны, соосно чипу. у микрона на эту тему аппликуха есть. и не забывайте, что спартан6, если мне память не изменяет, максимум что умеет, это всего ддр3-800, т.е.400МГц, а это частота, которая может прощать очень многое. В целом все ок, но просто необычно.

Для LVDS 1W не пройдет, нужно как минимум 2.5W, по правилам 3W. Для не LVDS на коротких трассах при большой плтности можно 1W.

ДА ддр3-800, т.е.400МГц, но не нужно забывать про скрорость нарастания фронтов, где требования до 5 и 7 гармоники от ваших 400 доходят.

На тех шинах 400Мгц не максимальная частота, если спектр посмотрите.

Наиболее правильно отделять не в единицах ширины трассы, а в расстоянии до следующего опорного слоя, т.е. H- итого "безопасность" начинается с 3H, но для спартана можно и 2H спокойно на таких дистанциях. Меньше уже не стоит

Не имеет значения в чем считать, в ширине или высоте. Они связаны одним и тем же коэффициентом, для внешнего слоя, например, 1.8 (для внутреннего не считал, но тоже какая-то константа). Т.е. для одного и того же импеданса W/H=1.8. Просто в единицах Н получается допустимо меньшее расстояние между трассами, чем в единицах W. В те самые 1.8 раза меньше. И во столько же раз больше места на трассировку

Цитата

Не имеет значения в чем считать, в ширине или высоте.

Да ничего подобного- в расчете кростолка наибольший вклад дает в т.ч. rise time и расстояние до опоры. Разделение же по ширине трасс это rule of thumb из дремучих времен.

Вы помнится упоминали что с приборами интела работаете- посмотрите у них бумаги, там хорошее объяснение присутствует. А вот насчет коэффициента хотелось бы подробнее послушать.

Да ничего подобного- в расчете кростолка наибольший вклад дает в т.ч. rise time и расстояние до опоры. Разделение же по ширине трасс это rule of thumb из дремучих времен.

Вы помнится упоминали что с приборами интела работаете- посмотрите у них бумаги, там хорошее объяснение присутствует. А вот насчет коэффициента хотелось бы подробнее послушать.

Вы помнится упоминали что с приборами интела работаете- посмотрите у них бумаги, там хорошее объяснение присутствует. А вот насчет коэффициента хотелось бы подробнее послушать.

Все так, и с расстоянием до опоры тоже. Просто меняя это расстояние придется менять и ширину трассы, чтобы сохранить нужный импеданс - чем выше до опоры, тем шире трасса. Вот об их соотношении я и написал, но ошибся. Зависимость есть, но оно зависит от многих факторов, и с изменением высоты до опоры ширина меняется, но не совсем линейно и конечно не с соотношением 1:1.8, как написал выше(это был частный случай). Так что комментарий снят, был не прав.

Цитата

Наиболее правильно отделять не в единицах ширины трассы, а в расстоянии до следующего опорного слоя

Плюсую. Раз уж зашел разговор

Цитата

To keep the near-end noise below 5% for worst-case coupling in a bus, separations should be at least two times the line width.

Кроме того:

Цитата

There's no far-end crosstalk in striplines

Так что в рассматриваемой конфигурации, когда вся трассировка по сути выполнена на внутренних слоях, для минимальных зазоров вполне можно использовать правило 2W. Но если место позволяет, то можно и больше конечно.

Цитата

To keep the near-end noise below 5% for worst-case coupling in a bus, separations should be at least two times the line width.

Если я хорошо помню ту бумажку(примерно такой аналог) там даже есть рисунки на которых видно как при разделении трасс на величины ширины дорог ожидаемо снижается расстояние до опоры. Но вообще разговор вроде шел за то чтобы адекватно использовать внешние слои, т.е. делать микрострипы которые как раз подвержены FEXT. Если я что пропустил то безусловно приношу извинения

Цитата

There's no far-end crosstalk in striplines

Ну, с этим никто не спорит

Я почему упомянул про дремучесть правила в разделении по ширинам трассы: немало "гайдов" применяют это дело к микрострипам. А там как раз надо на расстояние до опоры смотреть.

Ну и интол не зря упомянут- даже в открытом доступе есть вполне годные бумаги, в закрытом еще больше.

Цитата

Если я хорошо помню ту бумажку(примерно такой аналог)

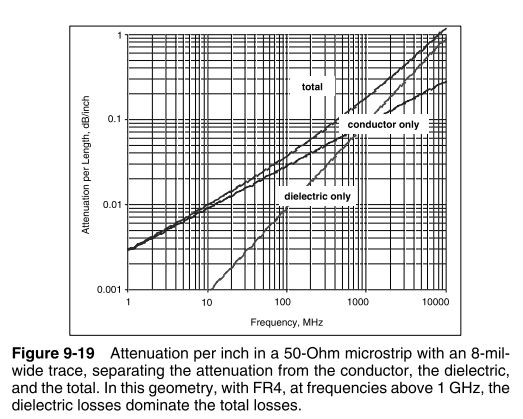

Открыл посмотреть, в самом начале встретил вот такую фразу "In high-speed serial links operating above 10 Gbps, losses are the dominant factor influencing

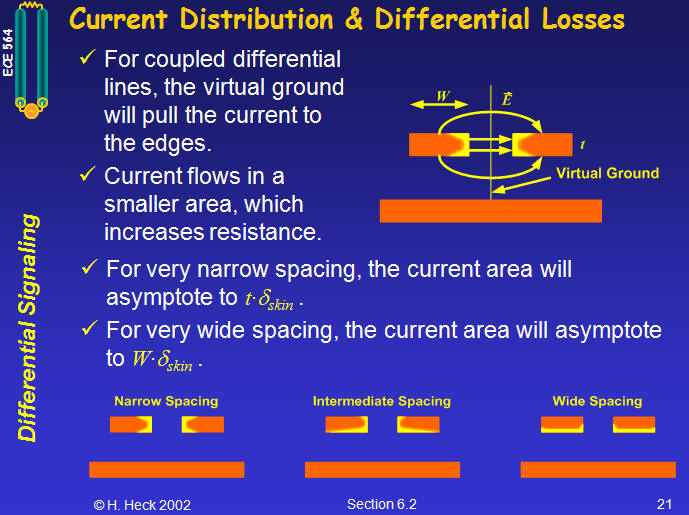

interconnect design. No matter how low the loss in the dielectric, conductor loss dominates the attenuation". Либо я чего-то не понял, либо тут автор что-то напутал, т.к. в его же книге (и не только в ней) вполне справедливо утверждается обратное и даже есть такой график

Цитата

Либо я чего-то не понял

Тут видимо имеется некоторый language barrier, давайте по порядку:

- в 10+G скоростях колхозный фр4 не кладут(нормальные люди), а кладут вестимо материалы с низкими потерями. В тоже самое время, потери есть- например от шероховатости фольги, или в дизайне пара с сильной связью в которой распределение токов идет к тонким краям между плечами, а не по "широкой" стороне. Где-то апликуха была, вспомню- приложу: наглядные картинки присутствовали.

- Богатин подчеркивает в начале предложения

Цитата

No matter how low the loss in the dielectric

т.е. говоря проще, проблему с потерями в диэлектрике в описываемом примере уже зарешали и к ней в данном случае не возваращаются, т.к. они незначительны на фоне остального.

- в тоже самое время в другом примере с другой задачей который вы привели, где как раз сигнал гоняется по фр4 он собственно и показывает, что как бы кто не изошрялся а проблемы с потерями в диэлектрике на тех частотах не зарулить никак, нужна замена на high-performance materials.

Достаточно грубое объяснение, но думаю понятно что противоречий нет.

Цитата

проблему с потерями в диэлектрике в описываемом примере уже зарешали

Да, похоже это и имелось ввиду

Именно- противоречие было бы если он написал в начале того предложения вместо

вот это

в контексте оглядки на не диэлектрические потери. А так просто разные примеры, из разных миров

Цитата

No matter how low the loss in the dielectric

вот это

Цитата

No matter how high the loss in the dielectric

в контексте оглядки на не диэлектрические потери. А так просто разные примеры, из разных миров

Добрый день. Ещё возник вопрос.

Я когда оттрасировал все адреса, не предусмотрел место под переходные для кондёров на землю и питание. А потом ещё вдобавок уменьшил кондёры и резисторы ии сдивнул ближе к ДДР. (см приложение 1)

Теперь при всем желании переходным напрямую я не могу их соединить. Если я сделаю вот такие полигоны в слое BOT (см приложение 2) чтобы подключить землю и питание, это как-то ухудшит работу памяти?

Я когда оттрасировал все адреса, не предусмотрел место под переходные для кондёров на землю и питание. А потом ещё вдобавок уменьшил кондёры и резисторы ии сдивнул ближе к ДДР. (см приложение 1)

Теперь при всем желании переходным напрямую я не могу их соединить. Если я сделаю вот такие полигоны в слое BOT (см приложение 2) чтобы подключить землю и питание, это как-то ухудшит работу памяти?

Сам полигон VTT может таким быть, а вот отсутствие переходных на землю близко к конденсаторам VTT... можно сказать, что этих конденсаторов там практически нет.

На работе шины это скажется, конечно, но не фатально.

На работе шины это скажется, конечно, но не фатально.

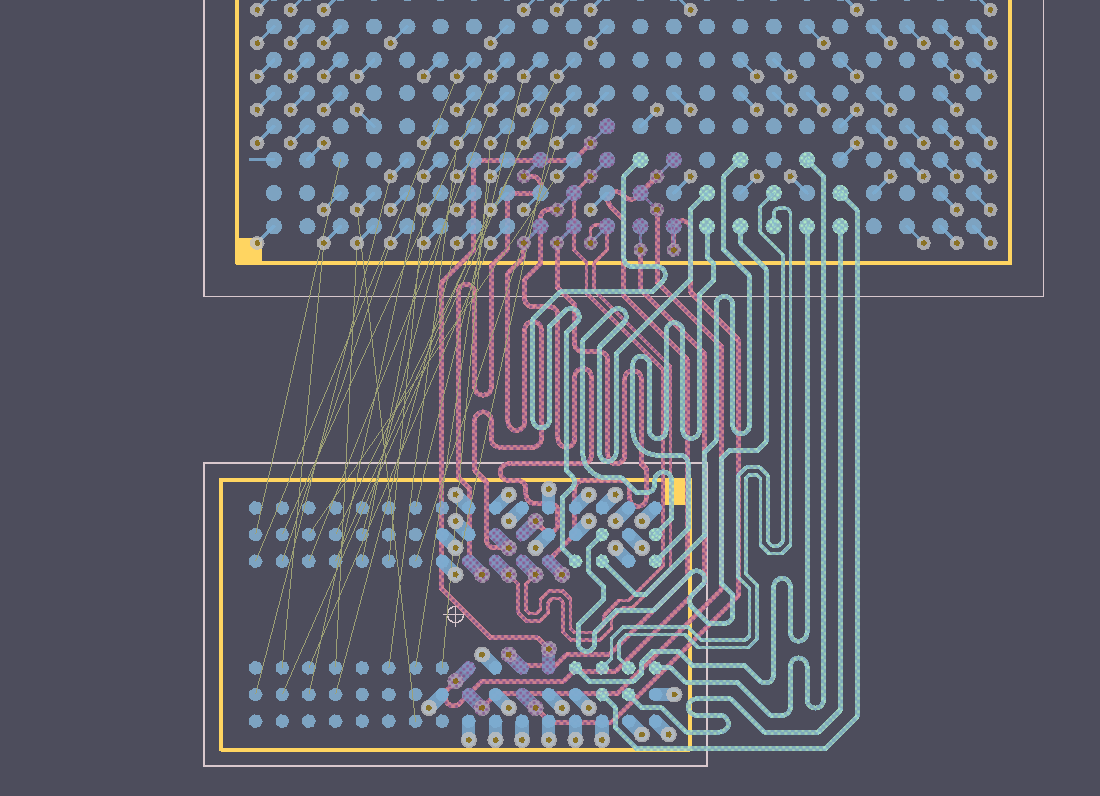

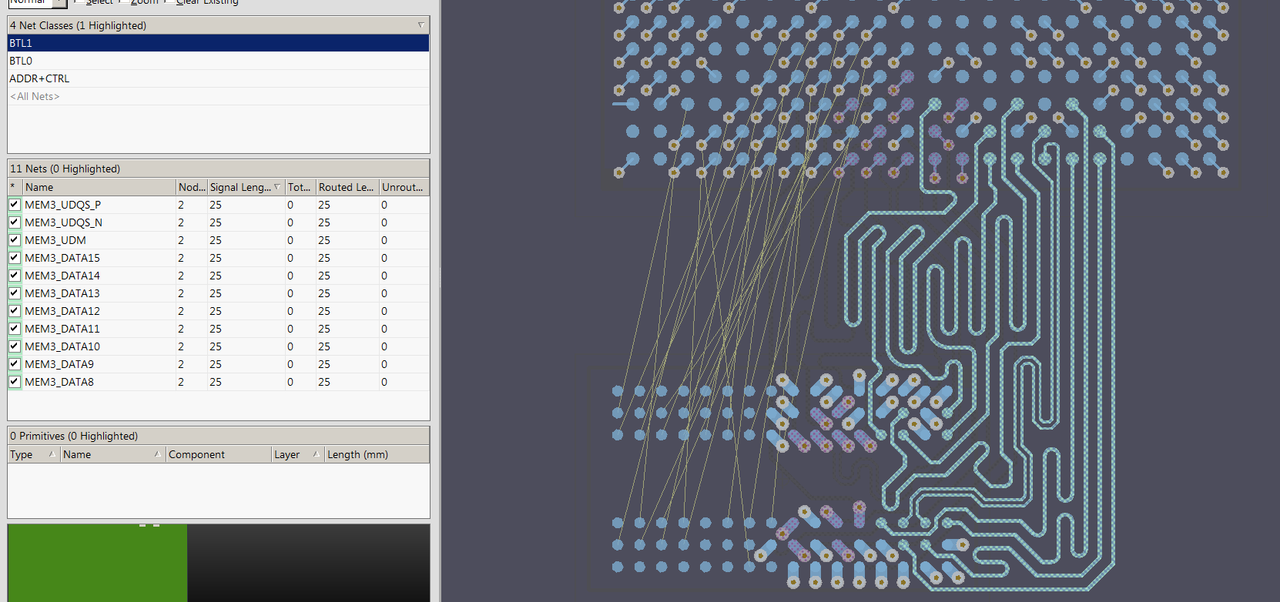

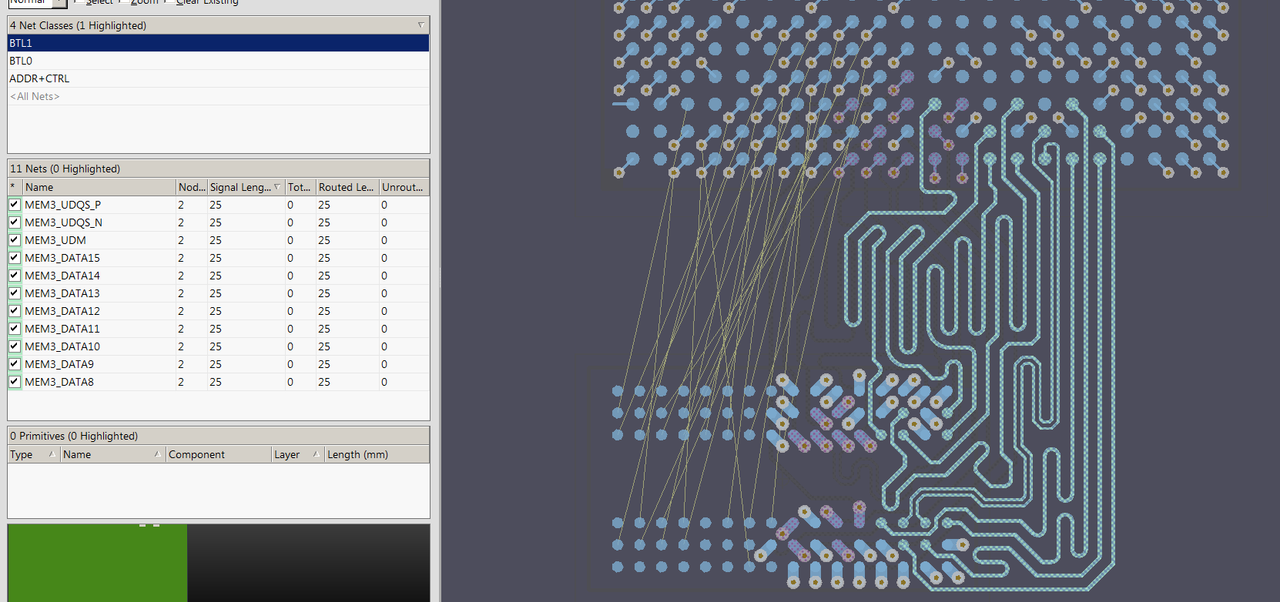

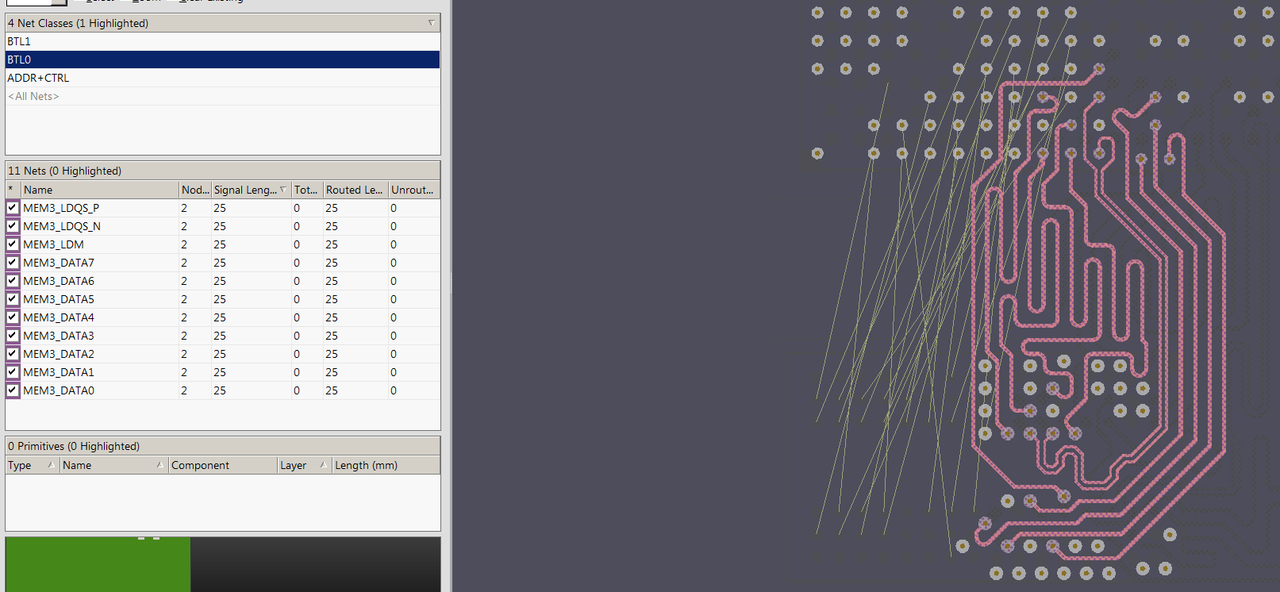

Некоторое время назад я добровольно вызвался показать пример на основе проекта тс- в контексте выравнивания не аккордеонами, с условием выкладывания в эту тему результата. В связи с этим представляю результаты на суд общественности, но перед этим несколько важных моментов:

- оглядываясь на ведение проекта(мне достался именно кусок со спартаном и ддр3 в формате аллегро), есть подозрение что не был настроен свапинг как таковой в самом сапр, т.е. процесс идет перестановкой нетлейблов. Могу ошибаться, но ни свап ни правила у меня в 17.2 не заработали .

.

- помимо этого, в оригинальном проекте используются сильно зарезанные пады у бга, например для ддр3 пады стоят 0.3мм.

- есть ряд сомнений касаемо расчетов импеданса и пр, т.к. в проекте используется FR4 c Dk=4.

В связи с этим в моем крайне скромном примере(больше пиво пил чем старался ) соблюдены следующие условия:

) соблюдены следующие условия:

- заимпортировал все в альтиум, т.к. под рукой был и он и библиотеки компонентов

- геометрия трасс взята с оригинального проекта, включая трассы толщиной 0.15мм

- зазор взят по расстоянию между фанаутами от внешних слоев(видно на скриншотах), т.е. более 2х толщин.

- фанауты специально не объединялись и не оттягивались от корпуса

- чтобы равномерно «нарастить мясо» было взято практически то же самое расстояние как и в оригинале, разница буквально пара мм. Для большей разницы в матчгруппе сделан сдвиг планки вбок.

- заложены «острова» под конденсаторы на боттоме со стороны байтлейнов

- пады ддр3 сделаны 0.43мм

- точность выравнивания взята сильно больше чем надо(все подведено под 25мм ровно)

- использовались только trombone, switchback, back-jog и bump. Аккордеоны а с ними и альтиумовский interactive length tuning не использовались, т.е. выравнивание «нарисовано».

Что имел намерение показать на этом примере(в основном сугубо для ТС):

- возможность развести все тромбонами и свичбэками

- возможность развести байтлейны на внешних слоях

- возможность сделать выравнивание существенно компактнее, в частности без заездов в зону адресом и управления

Думаю что хорошо заметно, что выравнивание легко переживет сдвиг вниз ддр3, т.к. основные наросты вертикальные. Поскольку под адреса есть 4 пустых слоя на разводку, отдельно обсуждать их не вижу смысла .

.

- оглядываясь на ведение проекта(мне достался именно кусок со спартаном и ддр3 в формате аллегро), есть подозрение что не был настроен свапинг как таковой в самом сапр, т.е. процесс идет перестановкой нетлейблов. Могу ошибаться, но ни свап ни правила у меня в 17.2 не заработали

- помимо этого, в оригинальном проекте используются сильно зарезанные пады у бга, например для ддр3 пады стоят 0.3мм.

- есть ряд сомнений касаемо расчетов импеданса и пр, т.к. в проекте используется FR4 c Dk=4.

В связи с этим в моем крайне скромном примере(больше пиво пил чем старался

- заимпортировал все в альтиум, т.к. под рукой был и он и библиотеки компонентов

- геометрия трасс взята с оригинального проекта, включая трассы толщиной 0.15мм

- зазор взят по расстоянию между фанаутами от внешних слоев(видно на скриншотах), т.е. более 2х толщин.

- фанауты специально не объединялись и не оттягивались от корпуса

- чтобы равномерно «нарастить мясо» было взято практически то же самое расстояние как и в оригинале, разница буквально пара мм. Для большей разницы в матчгруппе сделан сдвиг планки вбок.

- заложены «острова» под конденсаторы на боттоме со стороны байтлейнов

- пады ддр3 сделаны 0.43мм

- точность выравнивания взята сильно больше чем надо(все подведено под 25мм ровно)

- использовались только trombone, switchback, back-jog и bump. Аккордеоны а с ними и альтиумовский interactive length tuning не использовались, т.е. выравнивание «нарисовано».

Что имел намерение показать на этом примере(в основном сугубо для ТС):

- возможность развести все тромбонами и свичбэками

- возможность развести байтлейны на внешних слоях

- возможность сделать выравнивание существенно компактнее, в частности без заездов в зону адресом и управления

Думаю что хорошо заметно, что выравнивание легко переживет сдвиг вниз ддр3, т.к. основные наросты вертикальные. Поскольку под адреса есть 4 пустых слоя на разводку, отдельно обсуждать их не вижу смысла

EvilWrecker, спасибо за наглядный пример по тромбонам.

Так и есть

Это всё обсуждалось со специалистом, который монтирует бга в ИК печке, он рекомендовал пользоваться формулой 2/3*Dшара. Чем это чревато?

Я писал технологам PCBtech, мне выслали табличку с толщинами ядер, препрегов и их Dk, но заверили что всё это ориентировочно и актуально только для конкретного завода. И сколько там ядер и препрегов и каких именно положат китайцы только им известно. Поэтому да, я взял среднюю Dk=4. Если взять Dk=4.2 например, то импеданс изменится для внутреннего слоя на целых 3 Ома, это если считать в Polar. А если вбить все те же параметры в Сатурн, то он выдаст импеданс +-4 Ома от того что вышло в Polar.

В Top/Bottom у меня 0.15, а на внутренних -0.11мм

Это всё хорошо, но разговор был изначально про то, что мои адреса можно сократить в два раза:

А вы сократили байты с 32мм, до 25мм. При том что придвинули DDR ближе к Спартану

- оглядываясь на ведение проекта(мне достался именно кусок со спартаном и ддр3 в формате аллегро), есть подозрение что не был настроен свапинг как таковой в самом сапр, т.е. процесс идет перестановкой нетлейблов.

Так и есть

- помимо этого, в оригинальном проекте используются сильно зарезанные пады у бга, например для ддр3 пады стоят 0.3мм.

Это всё обсуждалось со специалистом, который монтирует бга в ИК печке, он рекомендовал пользоваться формулой 2/3*Dшара. Чем это чревато?

- есть ряд сомнений касаемо расчетов импеданса и пр, т.к. в проекте используется FR4 c Dk=4.

Я писал технологам PCBtech, мне выслали табличку с толщинами ядер, препрегов и их Dk, но заверили что всё это ориентировочно и актуально только для конкретного завода. И сколько там ядер и препрегов и каких именно положат китайцы только им известно. Поэтому да, я взял среднюю Dk=4. Если взять Dk=4.2 например, то импеданс изменится для внутреннего слоя на целых 3 Ома, это если считать в Polar. А если вбить все те же параметры в Сатурн, то он выдаст импеданс +-4 Ома от того что вышло в Polar.

В связи с этим в моем крайне скромном примере(больше пиво пил чем старался laughing.gif ) соблюдены следующие условия:

- геометрия трасс взята с оригинального проекта, включая трассы толщиной 0.15мм

- геометрия трасс взята с оригинального проекта, включая трассы толщиной 0.15мм

В Top/Bottom у меня 0.15, а на внутренних -0.11мм

Думаю что хорошо заметно, что выравнивание легко переживет сдвиг вниз ддр3, т.к. основные наросты вертикальные. Поскольку под адреса есть 4 пустых слоя на разводку, отдельно обсуждать их не вижу смысла biggrin.gif.

Это всё хорошо, но разговор был изначально про то, что мои адреса можно сократить в два раза:

В вашем дизайне спартан встает прекрасно байтлейнами на внешних слоях и частью адресов/команд там же, трассами гораздо короче 60мм(до 2х)....

А вы сократили байты с 32мм, до 25мм. При том что придвинули DDR ближе к Спартану

Цитата

Так и есть

Ну это вы зря- не лень каждый раз заново нетлист подгружать?

Цитата

Это всё обсуждалось со специалистом, который монтирует бга в ИК печке, он рекомендовал пользоваться формулой 2/3*Dшара. Чем это чревато?

Не знаю что это за специалист такой и что у него за формулы, но в случае со скриншота считалось по IPC- при этмо вышло даже чуть больше чем у самого микрона(у него 0.42мм). Самый минимум который использовал в своих дизайнах это 0.4мм- что касается рисков, то они такие же как и в любом другом случае непомерного вырезания падов.

Цитата

Поэтому да, я взял среднюю Dk=4. Если взять Dk=4.2 например, то импеданс изменится для внутреннего слоя на целых 3 Ома, это если считать в Polar. А если вбить все те же параметры в Сатурн, то он выдаст импеданс +-4 Ома от того что вышло в Polar.

Цитата

В Top/Bottom у меня 0.15

Ну так в приложенном примере и сделано на топе и боттоме- а если бы еще маски лежали удачнее в самом спартане, то и оба можно было бы воткнуть на топе.

Цитата

Это всё хорошо, но разговор был изначально про то, что мои адреса можно сократить в два раза:

Разумеется- и для того чтобы это сделать нужно выделить под них место: в частности сделать так чтобы байтлейны не "раздувало" и они не подпирали бы адреса с командами. У вас таргет на них идет на расстояние половины планки сбоку от ддр3, хотя все должно практически полностью умещаться между ней и спартаном. В случае приведенного примера как раз освобождено полностью все то место которое вы потратили на выравнивание, еще и остается на внешних слоях.

Ну это вы зря- не лень каждый раз заново нетлист подгружать?

На тот момент не разобрался как потом передавать изменения назад в схему.

Ну так в приложенном примере и сделано на топе и боттоме- а если бы еще маски лежали удачнее в самом спартане, то и оба можно было бы воткнуть на топе.

Да, не заметил что это топ

Спасибо

Еще небольшое дополнение выскажу касаемо тромбонов(а тем более с свичбэков)- как таковое их использование это один из вернейших признаков плотности и сложности дизайна. Очевидно что он больше всего нужен там, где места нет- т.к. такие же длины в той же площади аккордеонами не накрутить: при всем при этом надо понимать, что если в таком то дизайне удалось все заровнять аккордеонами, то с вероятностью близкой к 90% это возьмет автомат(в случае топ сапр). Более того, результат можно достаточно сильно оптимизировать в сторону уменьшения пустых островов, методология очень проста: выравнивание окружается boundary(например любой медный объект, хоть no net trace), далее соответственно они поджимаются в нужных участках и запускается новый проход автомата. Через несколько итераций можно получить результат который далеко не все т.н. синьоры смогут положить. В случае использования дуг все разумеется гораздо сложнее(а чаще и невыполнимо), но вот что касается тромбона и свичбэка то оглядываясь на приведенные ранее скриншоты автоматы так вообще не кладут. Есть и обратная сторона такого выравнивания(тромбонами)- в озвученных условиях это наиболее сложный и рискованный паттерн, в том смысле что очень велика вероятность положить не так таргет с соседями и заблокировать все свободное место. Если скажем делается дизайн аля HPC карточка на плис под PCIe слот и на ней скажем 4 ранка ддр4 уложенные memory down(притом честным флайбаем, без халявы типа кламшелов) то вероятность облажаться с таким выравниванием возрастает на несколько порядков.

Так очень легко оценить уровень дизайнов вообще- если например на плате нету courtyard-to-courtyard плэйсмента, или есть пустые острова от выравнивания, или все сделано аккордеонами то это вообще ни разу не плотный дизайн, сколько бы там ни было слоев и компонентов. Исключением можно назвать разве что некоторые супер оптимизированные корпуса(не надо много крутить выравнивание) а также дизайны типа 80+ слоев и 30к+ компонентов, там конечно уже другая история

Так очень легко оценить уровень дизайнов вообще- если например на плате нету courtyard-to-courtyard плэйсмента, или есть пустые острова от выравнивания, или все сделано аккордеонами то это вообще ни разу не плотный дизайн, сколько бы там ни было слоев и компонентов. Исключением можно назвать разве что некоторые супер оптимизированные корпуса(не надо много крутить выравнивание) а также дизайны типа 80+ слоев и 30к+ компонентов, там конечно уже другая история

Еще небольшое дополнение выскажу касаемо тромбонов(а тем более с свичбэков)- как таковое их использование это один из вернейших признаков плотности и сложности дизайна. Очевидно что он больше всего нужен там, где места нет- т.к. такие же длины в той же площади аккордеонами не накрутить

Можете пояснить, за счет чего тромбоны экономичнее аккордеонов? Только за счет срезов (или дуг) на верхушках меандров? Есть еще вариант выигрыша площади в случае одновиткового тромбона с выходом с той же стороны, что и вход, но это редкий частный случай.

Цитата

Можете пояснить, за счет чего тромбоны экономичнее аккордеонов?

Сугубо вопрос геометрии, т.к. существенно длиннее сама траектория выравнивания- даже небольшой загиб уже наращивает много длины. Есть хорошие картинки, там(22стр) достаточно неплохо видно разницу.

Цитата

Только за счет срезов (или дуг) на верхушках меандров?

Нет, тут именно фишка в том что проводник как бы повторяет сам себя, "по длинной стороне"- а в показанном примере просто удобнее было сделать дугами.

Цитата

Есть еще вариант выигрыша площади в случае одновиткового тромбона с выходом с той же стороны, что и вход, но это редкий частный случай.

Не могли бы вы пояснить что имеется в виду?

Переразвёл адреса и байты.

В результате Адреса -47мм, байты-26мм

В результате Адреса -47мм, байты-26мм

Все также плохой свапинг со стороны байтлейнов(+ также на внутренних слоях) и все такая же кривая раскидка адресов- зачем делать такой таргет?

В принципе, вы можете подзабить и дотянуть до нужного соотношение байтлейны а не адреса, раз такие проблемы именно с их таргетом- но тут все равно шило на мыло

В принципе, вы можете подзабить и дотянуть до нужного соотношение байтлейны а не адреса, раз такие проблемы именно с их таргетом- но тут все равно шило на мыло

У вас есть целевое соотношение длин от хилых- и поскольку место на адреса/команды вы используете максимально неэффективно, дотягивать до соотношения здесь проще длину байтлейнов. Хотя при таком свапинге и это может быть проблемой

Смог сократить адреса до 38мм, байты остались 25мм.

Что-то не вижу в Spartan-6 FPGA Memory Controller User Guide прямого указания на соотношение байтов и адресов.

Есть два требования:

Цитата

•CK and DQS trace lengths must be matched (±250 mil) to maximize setup and hold

margins.

• There must be a maximum ±50 ps electrical delay (±300 mil) between any

address/control signals and the associated CK and CK_N differential clock FPGA

output.

margins.

• There must be a maximum ±50 ps electrical delay (±300 mil) between any

address/control signals and the associated CK and CK_N differential clock FPGA

output.

Капитан очевидность заявляет следующее- по следу бумажки хилых:

- строб находится в матчгруппе в месте с маской и битами

- строб укладывается в соотношение к клоку

- клок связан соотношением с адресами/командами

Т.е в итоге у вас байтлейны имеют косвенную связь с адресами и командами

- строб находится в матчгруппе в месте с маской и битами

- строб укладывается в соотношение к клоку

- клок связан соотношением с адресами/командами

Т.е в итоге у вас байтлейны имеют косвенную связь с адресами и командами

Капитан очевидность заявляет следующее- по следу бумажки хилых:

- строб находится в матчгруппе в месте с маской и битами

- строб укладывается в соотношение к клоку

- клок связан соотношением с адресами/командами

Т.е в итоге у вас байтлейны имеют косвенную связь с адресами и командами

- строб находится в матчгруппе в месте с маской и битами

- строб укладывается в соотношение к клоку

- клок связан соотношением с адресами/командами

Т.е в итоге у вас байтлейны имеют косвенную связь с адресами и командами

Получается что с натяжкой я выполняю требования, если клок сделаю 31мм. (При адресах 38 и байтах-25мм)

CK and DQS trace lengths must be matched (±250 mil) to maximize setup and hold margins.

-Исходя из этого требования клок должен быть в интервале (18,65;31,25)

There must be a maximum ±50 ps electrical delay (±300 mil) between anyaddress/control signals and the associated CK and CK_N differential clock FPGAoutput.

-Исходя из этого требования клок должен быть в интервале (30,38;45,62)

Вы подождите с вычислениями, а лучше скажите какая у вас актуальная длина клока и обоих стробов?

Я не очень понимаю откуда берется такая рекомендация, но в общем случае, при числе чипов на шине большем чем один, оно не выполняется в принципе.

Точнее при 2-х чипах еще как-то можно попытаться его выполнить, но это будет весьма непросто, а при 4-х совсем невозможно.

Точнее при 2-х чипах еще как-то можно попытаться его выполнить, но это будет весьма непросто, а при 4-х совсем невозможно.

Так у спартана 6 далеко не самый могучий контроллер памяти, а что касается именно количества планок vs возможности выдержать эти констрейны, то тут вы конечно правы: в связи с этим на одной 16 битной шине там и сидит сугубо одна 16 битная планка.

А мне не очень, зачем их наращивать, если я могу просто сократить клок до 31мм? Тогда требования выполнятся

Клок находится в соотношении с командами и адресами, соответственно меняя клок изменятся и они- оглядываясь на то какой у вас там таргет, задача подгонки клока выглядит более трудоемкой чем подгонка байтлейнов. Но если вам проще зарулить именно клок, то нет проблем- возражения с моей стороны невозможны

Клок находится в соотношении с командами и адресами, соответственно меняя клок изменятся и они- оглядываясь на то какой у вас там таргет, задача подгонки клока выглядит более трудоемкой чем подгонка байтлейнов. Но если вам проще зарулить именно клок, то нет проблем- возражения с моей стороны невозможны

в этом соотношении?

Цитата

There must be a maximum ±50 ps electrical delay (±300 mil) between anyaddress/control signals and the associated CK and CK_N differential clock FPGAoutput.

Да, оно самое

А насколько оно жёсткое?

Просто в тех же рекомендациях на Спартан написано:

Цитата

• Only internal PCB layers should be used to route memory interface signals between the FPGA and memory devices. Breakout vias to connect component balls are excluded from this requirement.

А вы байты на внешних слоях провели

Цитата

А насколько оно жёсткое?

Ну, оглядываясь на число то наверное не очень жесткое, благо 300 мил это не 30

Цитата

Просто в тех же рекомендациях на Спартан написано:

Что из себя представляют рекомендации хилых- там время от времени проскальзывает фраза о том, что они составлены для типа 100% предсказуемо успешного результата в случае их выполнения, т.е. с серьезным запасом. Хорошим примером является требование по количеству конденсаторов в питании для такого-то корпуса, которое по факту завышено в несколько раз. Что касается внешних слоев, то разводить внутри конечно "безопаснее", но если делать правильно на внешних то никакого криминала нет и не может быть: на топе и боттоме разводят гораздо более высокоскоростную память без каких-либо проблем.

Касаемо именно вашего случая: на моей памяти есть люди которые успешно и не очень играли с timing margin в спартане, однако поскольку это ваш явно первый дизайн с ддр3 то лезть в эту тему пока что не рекомендую, тем более что озвученные в бумаге цифры легко реализуемы.

Ну, оглядываясь на число то наверное не очень жесткое, благо 300 мил это не 30  Вопрос я понимаю к тому что вам не удается выдержать ограничения которые хотят хилые?

Вопрос я понимаю к тому что вам не удается выдержать ограничения которые хотят хилые?

Что из себя представляют рекомендации хилых- там время от времени проскальзывает фраза о том, что они составлены для типа 100% предсказуемо успешного результата в случае их выполнения, т.е. с серьезным запасом. Хорошим примером является требование по количеству конденсаторов в питании для такого-то корпуса, которое по факту завышено в несколько раз. Что касается внешних слоев, то разводить внутри конечно "безопаснее", но если делать правильно на внешних то никакого криминала нет и не может быть: на топе и боттоме разводят гораздо более высокоскоростную память без каких-либо проблем.

Касаемо именно вашего случая: на моей памяти есть люди которые успешно и не очень играли с timing margin в спартане, однако поскольку это ваш явно первый дизайн с ддр3 то лезть в эту тему пока что не рекомендую, тем более что озвученные в бумаге цифры легко реализуемы.

Что из себя представляют рекомендации хилых- там время от времени проскальзывает фраза о том, что они составлены для типа 100% предсказуемо успешного результата в случае их выполнения, т.е. с серьезным запасом. Хорошим примером является требование по количеству конденсаторов в питании для такого-то корпуса, которое по факту завышено в несколько раз. Что касается внешних слоев, то разводить внутри конечно "безопаснее", но если делать правильно на внешних то никакого криминала нет и не может быть: на топе и боттоме разводят гораздо более высокоскоростную память без каких-либо проблем.

Касаемо именно вашего случая: на моей памяти есть люди которые успешно и не очень играли с timing margin в спартане, однако поскольку это ваш явно первый дизайн с ддр3 то лезть в эту тему пока что не рекомендую, тем более что озвученные в бумаге цифры легко реализуемы.

В итоге получилось что байты около 25мм, Адреса-35мм, а клок 31мм. В интервал уложился. Просто было интересно, не зря ли заморачивался.

В итоге получилось что байты около 25мм, Адреса-35мм, а клок 31мм. В интервал уложился. Просто было интересно, не зря ли заморачивался.

Если стробы в обоих байтах 25мм то да, уложились практически впритык

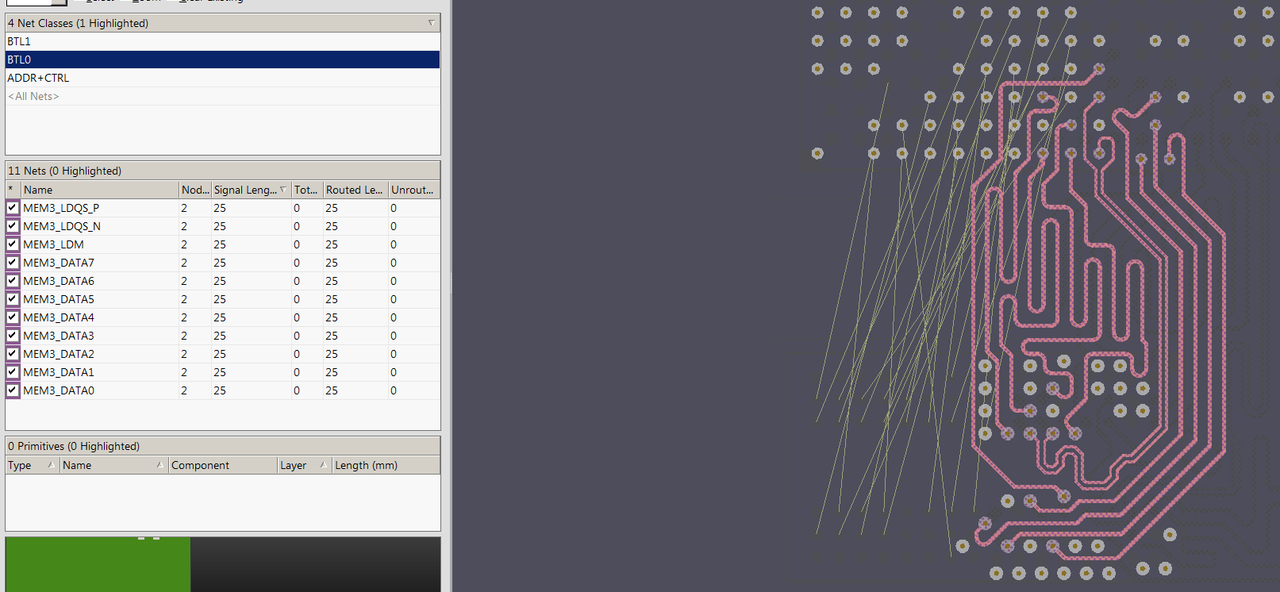

А есть картинки?

Если стробы в обоих байтах 25мм то да, уложились практически впритык  Заморачивались не напрасно т.к. при ваших вводных это повышает шансы на получение работоспособного дизайна.

Заморачивались не напрасно т.к. при ваших вводных это повышает шансы на получение работоспособного дизайна.

А есть картинки?

А есть картинки?

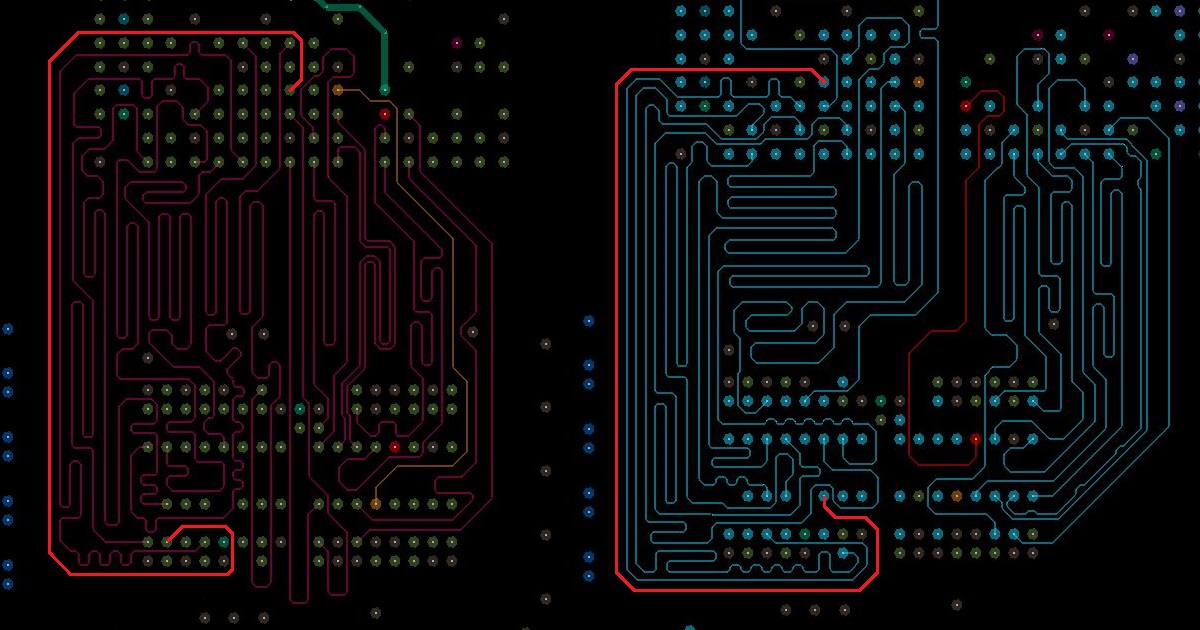

Вот.

(Кстати, у второй памяти смог адреса с клоком сделать 31мм, а байты -25)

Цитата

Кстати, у второй памяти смог адреса с клоком сделать 31мм, а байты -25

Мне вот интересно стало- вы приводите круглые числа, в ноль что ли выравниваете? Точно нету никакого tolerance?

Цитата

Вот.

Некоторый прогресс в геометрии есть, хотя конечно суть та же самая- но главное что в числа уложились

Для просмотра полной версии этой страницы, пожалуйста, пройдите по ссылке.