Цитата(Flip-fl0p @ May 21 2018, 20:17)

Поскольку полного кода я не вижу, я предположил, что вы создали свой модуль с именем DFF. А этого делать крайне нежелательно.

Это как ?

Вообще было бы неплохо, чтобы Вы полный текст проекта сюда выложили. Обычно для RTL симуляции библиотек надо минимум. И тип чипа вообще роли играть не должен !

Вот код одного из модулей:

CODE

module ram_blocks(

input clk,

input [15:0]addr,

input [15:0]data,

input wr,

output [15:0]data_1,

output [15:0]data_2,

output [15:0]data_3,

output [15:0]data_4,

output [15:0]data_5,

output [15:0]data_6,

output [15:0]data_7,

output [15:0]data_8,

output [15:0]data_9,

output [15:0]data_10,

output [15:0]data_11,

output [15:0]data_12,

output [15:0]data_13,

output [15:0]data_14,

output [15:0]data_15,

output [15:0]data_16);

wire s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15,s16;

wire w_VCC;

assign w_VCC = 1'b1;

AND2 AND2_01(.IN1(addr[0]), .IN2(wr), .OUT(s1));

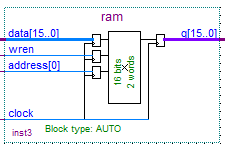

ram ram_01(.data(data), .wren(s1), .address(w_VCC), .clock(clk), .q(data_1));

AND2 AND2_02(.IN1(addr[1]), .IN2(wr), .OUT(s2));

ram ram_02(.data(data), .wren(s2), .address(1'b1), .clock(clk), .q(data_2));

AND2 AND2_03(.IN1(addr[2]), .IN2(wr), .OUT(s3));

ram ram_03(.data(data), .wren(s3), .address(1'b1), .clock(clk), .q(data_3));

AND2 AND2_04(.IN1(addr[3]), .IN2(wr), .OUT(s4));

ram ram_04(.data(data), .wren(s4), .address(1'b1), .clock(clk), .q(data_4));

AND2 AND2_05(.IN1(addr[4]), .IN2(wr), .OUT(s5));

ram ram_05(.data(data), .wren(s5), .address(1'b1), .clock(clk), .q(data_5));

AND2 AND2_06(.IN1(addr[5]), .IN2(wr), .OUT(s6));

ram ram_06(.data(data), .wren(s6), .address(1'b1), .clock(clk), .q(data_6));

AND2 AND2_07(.IN1(addr[6]), .IN2(wr), .OUT(s7));

ram ram_07(.data(data), .wren(s7), .address(1'b1), .clock(clk), .q(data_7));

AND2 AND2_08(.IN1(addr[7]), .IN2(wr), .OUT(s8));

ram ram_08(.data(data), .wren(s8), .address(1'b1), .clock(clk), .q(data_8));

AND2 AND2_09(.IN1(addr[8]), .IN2(wr), .OUT(s9));

ram ram_09(.data(data), .wren(s9), .address(1'b1), .clock(clk), .q(data_9));

AND2 AND2_10(.IN1(addr[9]), .IN2(wr), .OUT(s10));

ram ram_10(.data(data), .wren(s10), .address(1'b1), .clock(clk), .q(data_10));

AND2 AND2_11(.IN1(addr[10]), .IN2(wr), .OUT(s11));

ram ram_11(.data(data), .wren(s11), .address(1'b1), .clock(clk), .q(data_11));

AND2 AND2_12(.IN1(addr[11]), .IN2(wr), .OUT(s12));

ram ram_12(.data(data), .wren(s12), .address(1'b1), .clock(clk), .q(data_12));

AND2 AND2_13(.IN1(addr[12]), .IN2(wr), .OUT(s13));

ram ram_13(.data(data), .wren(s13), .address(1'b1), .clock(clk), .q(data_13));

AND2 AND2_14(.IN1(addr[13]), .IN2(wr), .OUT(s14));

ram ram_14(.data(data), .wren(s14), .address(1'b1), .clock(clk), .q(data_14));

AND2 AND2_15(.IN1(addr[14]), .IN2(wr), .OUT(s15));

ram ram_15(.data(data), .wren(s15), .address(1'b1), .clock(clk), .q(data_15));

AND2 AND2_16(.IN1(addr[15]), .IN2(wr), .OUT(s16));

ram ram_16(.data(data), .wren(s16), .address(1'b1), .clock(clk), .q(data_16));

endmodule

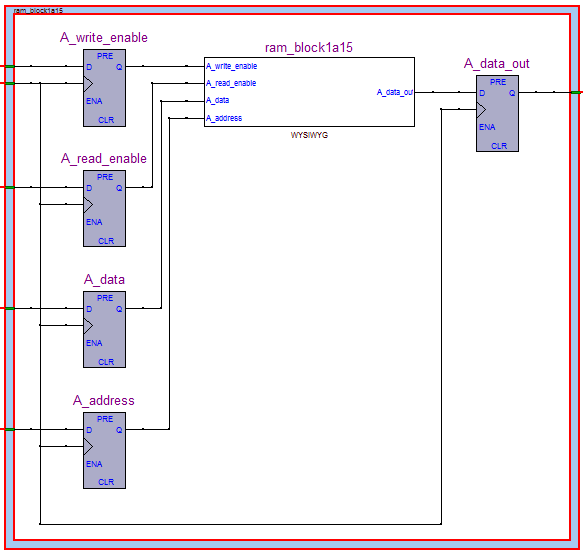

В модуле используется элемент AND2, экземпляры которого я создаю. Но элемент AND2 так же как и DFF не могу найти ни в одной из библиотек, подключал уже все файлы из папки C:\altera\15.0\modelsim_ase\altera\verilog\src

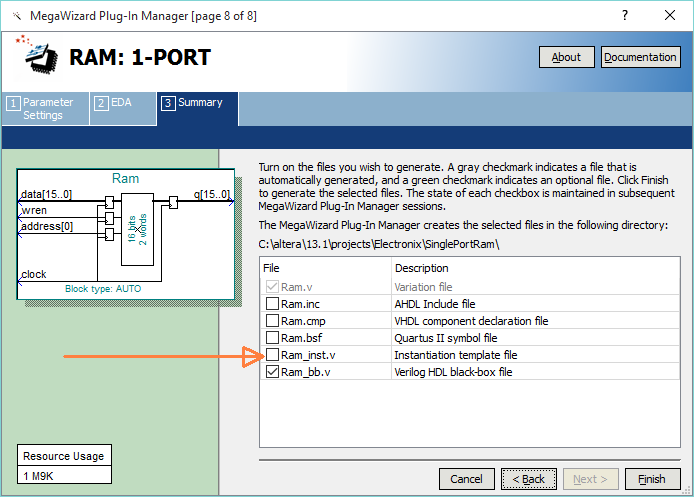

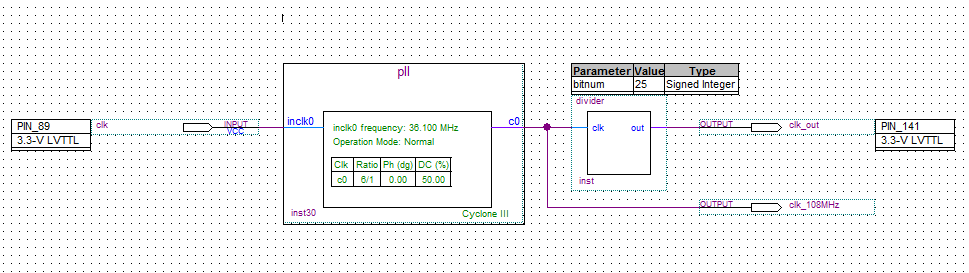

Я подозреваю, что это из за того, что проект разрабатывался в Quartus 9.1, а ModelSim используется от версии квартуса 15.0 где отсутствует библиотека для cyclone III. Как мне быть? Перейти на Quartus 13.1? Не очень бы хотелось - как показывает практика - чем выше версия квартуса - тем больше тормозов и времени на компиляцию.

Warning from admin:

Используйте codebox для длинных цитат программного кода!