Добрый день, для своего хобби-проекта нужно подключить к CycloneIII(потенциально EP3C16Q240C8N) побольше памяти (2Гб и больше).

Дано:

1) Можно делать 2-х слойные платы с дорогами 0.2мм(но если очень хочется, можно и 0.1). Вижу что обычно делают 4 слоя. Если с обоих сторон покрыть лаком и слоем металлизации как экраном - поможет ли?

2) Скорость работы памяти не критична, хоть 50Мгц уже что-то, главное количество памяти (тут как раз у SRAM/SDRAM/DDR1 проблемы).

3) Хотелось бы обойтись без BGA-чипов памяти, возможно ли использовать стандартные планки памяти с разъемами? Возможность воткнуть 4Гб планку памяти - вот предел мечтаний :-)

4) При необходимости FPGA можно взять дороже.

Насколько это реально для относительного новичка? (С FPGA занимался последний раз лет 8 назад, схему на 1млн LE сделал и отладил, никуда не влезла :-) ).

Или с такими ограничениями остается опустить руки, и подключать тучу 8ns SRAM-ок? (максимум что видел K6R4008C1D на 4Мбит, с большей емкостью только медленные)

Update: Удалил DDR3, там похоже только StratixIII поможет :-)

Полная версия этой страницы: CycloneIII+DDR2 - оценка трудности

Форум разработчиков электроники ELECTRONIX.ru > Программируемая логика ПЛИС (FPGA,CPLD, PLD) > Работаем с ПЛИС, области применения, выбор

Дано:

1) Можно делать 2-х слойные платы с дорогами 0.2мм. Вижу что обычно делают 4 слоя. Если с обоих сторон покрыть лаком и слоем металлизации как экраном - поможет ли?

1) Можно делать 2-х слойные платы с дорогами 0.2мм. Вижу что обычно делают 4 слоя. Если с обоих сторон покрыть лаком и слоем металлизации как экраном - поможет ли?

DDR2/DDR3 бывает исключительно в корпусах BGA с шагом 0.8мм, поэтому с геометрией 0.2мм гарантировано не уложитесь.

3) Хотелось бы обойтись без BGA-чипов памяти, возможно ли использовать стандартные планки памяти с разъемами? Возможность воткнуть 4Гб планку памяти - вот предел мечтаний :-)

Без BGA не найдете, разве что малоизвестная нестандартная (т.е. не JEDEC-кая будет) экзотика. Использование готовых DIMM-ов - вариант, можно попробовать.

А Вы уверены что Вам RAM надо, т.е. многократная запись точно нужна? При 50МГц уже многие NAND работать смогут, 2ГБ для них детский объем.

Upd: DDR3 еще новые Спартаны-6 поддерживают, если без GTX то по цене доступно выйдет.

Многие NAND уже умеют работать 83МГц DDR (и это я еще в каталог high speed не смотрел), так что вам на самом деле имеет смысл на них глянуть. На двуслойной плате DDR память не делается, DIMM вы не разведете в двух слоях и не подключите к QFP корпусу.

Spartan-6 по цене действительно подходят, но не-БГА у них только крошки до 9к Logical Cells.

Нужно именно память, на FPGA - процессор.

А если с перемычками? Это же один экземпляр, лишние 10-20 минут на перемычки есть.

По идее качество сигнала не должно быть хуже, чем от дорог на соседних слоях...

Нужно именно память, на FPGA - процессор.

Цитата

На двуслойной плате DDR память не делается, DIMM вы не разведете в двух слоях и не подключите к QFP корпусу.

А если с перемычками? Это же один экземпляр, лишние 10-20 минут на перемычки есть.

По идее качество сигнала не должно быть хуже, чем от дорог на соседних слоях...

Для планки требуется 128 ног, даже если не учитывать их спецназначение. В QFP столько найдется выводов у ПЛИС?

Если не секрет, что за чудо было?

Аппаратная реализация RC5-64 для проекта http://www.distributed.net/rc5/

Проверяло 1 ключ за такт - было огромное кол-во стадий конвейера.

Счастливые университетские годы :-)

Это же один экземпляр, лишние 10-20 минут на перемычки есть.

Если это один экземпляр - то практически всегда проще и нередко даже дешевле купить готовый кит. DIMM вы не подключите к QFP - читайте внимательно даташиты (или форум; несколькими топиками ниже невозможность подключения DIMM к Циклону в корпусе BGA780 раскрыта чуть более, чем полностью): там нельзя подключать скоростную память куда попало.

Цитата

несколькими топиками ниже невозможность подключения DIMM к Циклону в корпусе BGA780 раскрыта чуть более, чем полностью): там нельзя подключать скоростную память куда попало.

Да нет, я видел отладку, в топике ниже вроде приводил, там к ц3 BGA780 подключен SODIMM. Но суть не в этом, для QFP действительно о такой разрядности говорить нечего. Хотя кто-то, помнится, собирался подключить 8 бит DDR к ней...

Не подскажите ссылку где говорят что нельзя?

Пока вижу

На форуме альтеры нашел что SODIMM DDR2 можно подключить к 484-контактному циклону

В общем понятно, к 240-контактному чипу DIMM точно не подключить.

Тогда с какой толщиной дорог разводятся отдельные DDR2 чипы памяти, и насколько реально заставить работать отдельные чипы на обычной двухсторонней плате?

(Думаю припаять BGA память я еще смогу, а вот 484-контактный FPGA вряд ли :-) )

Сколько-битная память тогда влезет по идее к 240-контактному циклону?

Пока вижу

Цитата

P.S. Кстати насчет DDR2 DIMM - там каждый байт идет со своим синхросигналом, поэтому шина и размазывается без проблем по нескольким банкам.

На форуме альтеры нашел что SODIMM DDR2 можно подключить к 484-контактному циклону

В общем понятно, к 240-контактному чипу DIMM точно не подключить.

Тогда с какой толщиной дорог разводятся отдельные DDR2 чипы памяти, и насколько реально заставить работать отдельные чипы на обычной двухсторонней плате?

(Думаю припаять BGA память я еще смогу, а вот 484-контактный FPGA вряд ли :-) )

Сколько-битная память тогда влезет по идее к 240-контактному циклону?

А реально чем не подходит ONFI флеша: 14 лап на объём в десяток гигабит

Флешу для стандарта ONFI 1.0 в принципе реально заказать (если через контору). Для ONFI 1.0 - можно на 100МГц данные в потоке гонять.

Если не устраивает скорость - поставьте 2+ штуки и она пропорционально увеличится

Флешу для стандарта ONFI 1.0 в принципе реально заказать (если через контору). Для ONFI 1.0 - можно на 100МГц данные в потоке гонять.

Если не устраивает скорость - поставьте 2+ штуки и она пропорционально увеличится

А реально чем не подходит ONFI флеша: 14 лап на объём в десяток гигабит

Флешу для стандарта ONFI 1.0 в принципе реально заказать (если через контору). Для ONFI 1.0 - можно на 100МГц данные в потоке гонять.

Если не устраивает скорость - поставьте 2+ штуки и она пропорционально увеличится

Флешу для стандарта ONFI 1.0 в принципе реально заказать (если через контору). Для ONFI 1.0 - можно на 100МГц данные в потоке гонять.

Если не устраивает скорость - поставьте 2+ штуки и она пропорционально увеличится

Это процессор, он и читает и пишет, много и быстро.

Ну и у флеши очень неприятная латентность при записи, особенно если флеш с ужасом понимает, что перед записью блок надо бы еще и стереть :-)

Ну тогда вам дорога в бга корпуса и ддр

На 4-х слойке думаю без проблем осилите ддр2 в корпусах.

Вот на счёт содим - тут вроде 6 слоёв как нужно.

На 4-х слойке думаю без проблем осилите ддр2 в корпусах.

Вот на счёт содим - тут вроде 6 слоёв как нужно.

Ну тогда вам дорога в бга корпуса и ддр.

На 4-х слойке думаю без проблем осилите ддр2 в корпусах.

Вот на счёт содим - тут вроде 6 слоёв как нужно.

На 4-х слойке думаю без проблем осилите ддр2 в корпусах.

Вот на счёт содим - тут вроде 6 слоёв как нужно.

Больше интересует реальность DDR2 чипов на двухслойке, возможно с перемычками.

Если плату 4-6 слоев делать, то уже и FPGA BGA впаять можно - но тогда почти все придется делать не самому :-)

На сколько я знаю таким никто не занимался  Вам видимо предстоит долго и нудно гуглить

Вам видимо предстоит долго и нудно гуглить

Кстати о какой быстроте идёт речь когда частота прожекта 50МГц?? Или у вас ключевой параметры для памяти это latency?

Или у вас ключевой параметры для памяти это latency?

Кстати о какой быстроте идёт речь когда частота прожекта 50МГц??

На сколько я знаю таким никто не занимался  Вам видимо предстоит долго и нудно гуглить

Вам видимо предстоит долго и нудно гуглить

Кстати о какой быстроте идёт речь когда частота прожекта 50МГц?? Или у вас ключевой параметры для памяти это latency?

Или у вас ключевой параметры для памяти это latency?

Кстати о какой быстроте идёт речь когда частота прожекта 50МГц??

Ну, DDR2 50Мгц(впрочем по стандарту минимум 125Мгц) на 16-32 бита и флеш память... По скорости небо и земля :-)

Про нудное гугление - эт само собой, и теребить людей придется долго как местных так и буржуев :-)

Сейчас интересны именно мнения о реализуемости опытных разработчиков.

Ну, DDR2 50Мгц(впрочем по стандарту минимум 125Мгц) на 16-32 бита и флеш память... По скорости небо и земля :-)

Ну не скажите..

Флеша имеет 14 лап, стандарт 1.0 позволяет работать на 10нс, шина данных камня - байт, ставите 4 шутки для 32бит - уже получаем 10/4нс на чтение в потоке, ну там +/-.

На запись в занятые сектора для уменьшения latency тоже можно поизголяться

Просто, по-моему вы не в ту сторону копаете...

NAND как единственная память для процессора не подойдет - там латентность случайного доступа будет ужасной. Надо поставить DDR (первую) в планарном корпусе и NAND, DDR будет как бы большим кэшем. Плату лучше делать в четыре слоя - это будет гарантировать успех. NAND ставьте SLC, это возможно позволит любительскому проекту прожить сколько-то без wear leveling.

Ну, DDR2 50Мгц(впрочем по стандарту минимум 125Мгц)

А кстати да - для DDR2 минимальный период тактовой 8 нс, и во всех даташитах это прописано. ИМХО, на меньшей частоте есть риск налететь на некорректную работу внутренней DLL чипов памяти. Или знаете реальные примеры где DDR2 на маленьких частотах работает?

BTW, а какая Вам разрядность памяти нужна? Чтобы оно там в один банк (chip select) влезло, а то шина данных DDR из топологически простой "точка-точка" может в бнопню превратиться.

Вопрос с системой хранения не стоит - это будет микроконтроллер с SD картой через SPI, намного проще и быстрее в разработке чем ковыряться с NAND на низком уровне.

Стоит только вопрос с DDR2.

Разрядность - жестких ограничений нет, но чем больше - тем лучше :-) Отсюда и вопрос о том, какую разрядность удастся впихнуть с QFP корпусом.

Стоит только вопрос с DDR2.

Разрядность - жестких ограничений нет, но чем больше - тем лучше :-) Отсюда и вопрос о том, какую разрядность удастся впихнуть с QFP корпусом.

Вот теперь ясно почему вы так всячески отвергали NAND

На счёт ддр - посмотрите даташит и экселевский файл на 3-й циклон для верности, но если мне память не изменяет у QFP корпуса встречал x8

На счёт ддр - посмотрите даташит и экселевский файл на 3-й циклон для верности, но если мне память не изменяет у QFP корпуса встречал x8

Нашел, 4*8 в QFP корпус лезет на частоте до 150Мгц.

Остается вопрос о том, насколько реально развести BGA чипы памяти на 1/2 стороне платы.

И еще вот такой вопрос: а сколько чипов памяти можно на один канал повесить? Я так полагаю, тут можно и больше 2-х, т.к. частота маленькая...

Остается вопрос о том, насколько реально развести BGA чипы памяти на 1/2 стороне платы.

И еще вот такой вопрос: а сколько чипов памяти можно на один канал повесить? Я так полагаю, тут можно и больше 2-х, т.к. частота маленькая...

И еще вот такой вопрос: а сколько чипов памяти можно на один канал повесить? Я так полагаю, тут можно и больше 2-х, т.к. частота маленькая...

Если у вас будет четырехслойная плата - можно повесить сколько угодно, если правильно терминацию сделать. На двуслойной плате - молитесь, чтобы один чип заработал, 125 МГц DDR - это 4 ns на бит. HyperLynx освойте - вы сможете быстро давать прогноз по таким вопросам.

Не совсем понятно ваше нежелание использовать четырехслойку. Разводить на ней будет проще, монтаж такой же, стоит она ну в несколько раз подороже. Зато проблем с запуском будет на порядок меньше и надежность работы устройства будет намного больше.

Товарищ хочет все сделать на коленках за 2 копейки. Так не бывает, а если бывает - то только в сказках.

При работе с DDR2 нужно очень внимательно относится к трассировке. Даже если высокие скорости не нужны. Были проблемы при подключении DDR2 SO-DIMM к Cyclone II. Всего то, не выровняли проводники шины данных по длинне. Долго мучались пока запустили на частоте 160 Мгц, спасибо Альтере за гибкую структуру микросхем. На 2-х слойке развести DDR2 по моему не реально.

При работе с DDR2 нужно очень внимательно относится к трассировке. Даже если высокие скорости не нужны. Были проблемы при подключении DDR2 SO-DIMM к Cyclone II. Всего то, не выровняли проводники шины данных по длинне. Долго мучались пока запустили на частоте 160 Мгц, спасибо Альтере за гибкую структуру микросхем. На 2-х слойке развести DDR2 по моему не реально.

Товарищ хочет все сделать на коленках за 2 копейки. Так не бывает, а если бывает - то только в сказках.

При работе с DDR2 нужно очень внимательно относится к трассировке. Даже если высокие скорости не нужны. Были проблемы при подключении DDR2 SO-DIMM к Cyclone II. Всего то, не выровняли проводники шины данных по длинне. Долго мучались пока запустили на частоте 160 Мгц, спасибо Альтере за гибкую структуру микросхем. На 2-х слойке развести DDR2 по моему не реально.

При работе с DDR2 нужно очень внимательно относится к трассировке. Даже если высокие скорости не нужны. Были проблемы при подключении DDR2 SO-DIMM к Cyclone II. Всего то, не выровняли проводники шины данных по длинне. Долго мучались пока запустили на частоте 160 Мгц, спасибо Альтере за гибкую структуру микросхем. На 2-х слойке развести DDR2 по моему не реально.

Да, вы правы, именно на коленках и за 2 копейки, ибо это хобби а не на продажу.

Заказывать все на заводе и получать продукт, к которому не была приложена моя рука - совсем не интересно.

Известно следующее:

1) Чем больше слоев - тем хуже качество сигналов (много где видел). Пока не понятно почему считается что 4 лучше чем 2.

2) Чисто на 2-х слоях у меня нет цели делать, мне не лень запаять перемычки, качество сигналов на них не должно быть хуже чем на ПП - расстояние между проводниками всяко больше.

3) Насчет тайминга - опять же, писали что это не особо критично на этих частотах, главное с DQS угадать. Думаю, DQS точно сделаю проводом, длину которого можно подбирать.

Посмотрел в других ветках - в расстояние между пинами DDR2 чипов можно запихнуть дорогу на 0.127мм (и пустое место тоже по 0.127). Непросто для домашнего фото-способа.

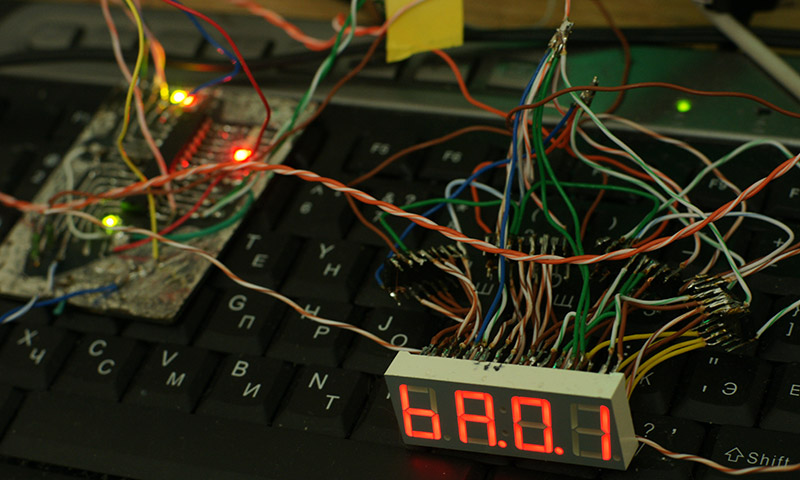

Впрочем, есть сумасшедший вариант :-) Видел как немаленький BGA чип был с подпаянными проводками к шарам, у DDR2 пинов не много, должно быть вполне реально :-) (блин, не могу найти фотку этого чуда)

Все три пронумерованных пункта являются чистым заблуждением. Что же касается толщины проводников под BGA - она чаще определяется не зазором между шариками, а зазором между via.

2)качество сигналов на них не должно быть хуже чем на ПП - расстояние между проводниками всяко больше.

Ну Вы хотя бы классику почитали - "Начальный курс черной магии - конструирование высокоскоростных цифровых устройств" Говарда Джонсона, тогда не делали бы таких сильных заявлений. И не тешьте себя надеждой что "частота маленькая - скорость низкая", важна не частота, а спектр сигнала, грубо говоря, фронты. Чипы DDR2 "заточены"под большие частоты, и скорость нарастания на линиях DQ запросто может быть 2V/нс и выше - и "звону" на Ваших перемычках будет "мама не горюй".

1) Чем больше слоев - тем хуже качество сигналов (много где видел). Пока не понятно почему считается что 4 лучше чем 2.

Вот на счет этого я могу поспорить. Многослойность нужна еще и для того что бы обеспечить волновое сопротивление проводника, например 50 Ом. Когда все проводники проводятся внутри, между опорными слоями земли и питания. Без этого терминаторы на линиях будут только ухудшать качество сигнала и приводить к повышению звона, а не на оборот. На 2-х слоях (да даже на 4-х) этого сделать не удастся. А на несогласованных линиях говорить о стабильной работе DDR2, даже на низких частотах бесполезно.

Известно следующее:

1) Чем больше слоев - тем хуже качество сигналов (много где видел). Пока не понятно почему считается что 4 лучше чем 2.

2) Чисто на 2-х слоях у меня нет цели делать, мне не лень запаять перемычки, качество сигналов на них не должно быть хуже чем на ПП - расстояние между проводниками всяко больше.

3) Насчет тайминга - опять же, писали что это не особо критично на этих частотах, главное с DQS угадать. Думаю, DQS точно сделаю проводом, длину которого можно подбирать.

Посмотрел в других ветках - в расстояние между пинами DDR2 чипов можно запихнуть дорогу на 0.127мм (и пустое место тоже по 0.127). Непросто для домашнего фото-способа.

Впрочем, есть сумасшедший вариант :-) Видел как немаленький BGA чип был с подпаянными проводками к шарам, у DDR2 пинов не много, должно быть вполне реально :-) (блин, не могу найти фотку этого чуда)

1) Чем больше слоев - тем хуже качество сигналов (много где видел). Пока не понятно почему считается что 4 лучше чем 2.

2) Чисто на 2-х слоях у меня нет цели делать, мне не лень запаять перемычки, качество сигналов на них не должно быть хуже чем на ПП - расстояние между проводниками всяко больше.

3) Насчет тайминга - опять же, писали что это не особо критично на этих частотах, главное с DQS угадать. Думаю, DQS точно сделаю проводом, длину которого можно подбирать.

Посмотрел в других ветках - в расстояние между пинами DDR2 чипов можно запихнуть дорогу на 0.127мм (и пустое место тоже по 0.127). Непросто для домашнего фото-способа.

Впрочем, есть сумасшедший вариант :-) Видел как немаленький BGA чип был с подпаянными проводками к шарам, у DDR2 пинов не много, должно быть вполне реально :-) (блин, не могу найти фотку этого чуда)

Да вам плата вообще не нужна тогда: можно все микросхемы кверху брюхом перевернуть (в том числе и БГА память), приклеить к листу фанеры и МГТФ-ом все межсоединения сделать.

З.Ы. В результате получится ваша мечта - плата с числом слоёв равным нулю и одними перемычками. Проблем вообще никаких: возратных токов нету, волнового сопротивления нету, перемычки сигнал не искажают, голова при разводке платы не болит. Плюс ещё можно на лету выравнивть длины дорожек путём выравнивания длин проводов из МГТФ.

P.S. Если не заработает купите бубен(только хороший, кожаный) и читайте про чёрную магию - книжка правильная.

Да вам плата вообще не нужна тогда: можно все микросхемы кверху брюхом перевернуть (в том числе и БГА память), приклеить к листу фанеры и МГТФ-ом все межсоединения сделать.  Дешево и сердито. Кстати тогда и ПЛИС можно в БГА брать - например можно заюзать Spartan6 со встроенным контроллером DDR3 - вообще супер девайс получится.

Дешево и сердито. Кстати тогда и ПЛИС можно в БГА брать - например можно заюзать Spartan6 со встроенным контроллером DDR3 - вообще супер девайс получится.

Проводами меня не испугать ;-)

Тут проводов похоже больше чем на 8 бит DDR2

Книгу про черную магию скачал, читаю :-)

Вот на счет этого я могу поспорить. Многослойность нужна еще и для того что бы обеспечить волновое сопротивление проводника, например 50 Ом. Когда все проводники проводятся внутри, между опорными слоями земли и питания. Без этого терминаторы на линиях будут только ухудшать качество сигнала и приводить к повышению звона, а не на оборот. На 2-х слоях (да даже на 4-х) этого сделать не удастся. А на несогласованных линиях говорить о стабильной работе DDR2, даже на низких частотах бесполезно.

На этот счет 2 мысли:

1) Открыл корпус, смотрю на разводку DDR2 на материнской плате - дороги идут по поверхности, никакого волнового канала.

2) Землю поверх дорог я могу сделать и без 4-х слойной платы - слой лака+слой металлизации посаженный на землю или приклеенная фольга.

Проводами меня не испугать ;-)

Тут проводов похоже больше чем на 8 бит DDR2

Книгу про черную магию скачал, читаю :-)

На этот счет 2 мысли:

1) Открыл корпус, смотрю на разводку DDR2 на материнской плате - дороги идут по поверхности, никакого волнового канала.

2) Землю поверх дорог я могу сделать и без 4-х слойной платы - слой лака+слой металлизации посаженный на землю или приклеенная фольга.

Тут проводов похоже больше чем на 8 бит DDR2

Книгу про черную магию скачал, читаю :-)

На этот счет 2 мысли:

1) Открыл корпус, смотрю на разводку DDR2 на материнской плате - дороги идут по поверхности, никакого волнового канала.

2) Землю поверх дорог я могу сделать и без 4-х слойной платы - слой лака+слой металлизации посаженный на землю или приклеенная фольга.

плохо читаете:

дороги идут на поверности а под ними непрерывный слой земли.

Если вы сможете нанести слой лака заданной толщины с точностью 10%, и знаете его диэлектрическую проницаемость на высоких частотах - то флаг вам в руки, а иначе бубен вам в помощь.

Про волновой канал и то что дорожки обязательно должны быть внутри - это байки от тех, кто слоёв в плате не считает.

И уж поверьте если китайцы смогли бы развести двухслойную плату с DDR2 - они бы это сделали. Они умудряются порой такие удивительные чудо-девайсы собирать из двух транзисторов, трёх кондёров и пустых мест под незапаянные детали.

2) Землю поверх дорог я могу сделать и без 4-х слойной платы - слой лака+слой металлизации посаженный на землю или приклеенная фольга.

Делайте. В конце концов, наши ограничения существуют только у нас в уме. Кто знает, может быть вам удастся сказать новое слово в схемотехнике и конструкции аппаратуры. Даже если это не заработает, вы многому научитесь. Желаю успеха.

Всего то, не выровняли проводники шины данных по длинне. Долго мучались пока запустили на частоте 160 Мгц, спасибо Альтере за гибкую структуру микросхем.

1).А можно подробней о выравнивании шины данных по длине?Мне нужно принять 14 бит данных,LVDS,DDR(не память),частота клока 280МГц.Разброс длин дорожек бит данных(макс минус мин) - 22мм.Это нормально или ещё нужно поровнять?Какой разброс длин вообще допустим?Вроде перекос распространения всего 66 ps при периоде 1800 ps.

2).Конструктор не может развести диффпары по данным в одном слое,если эти диффпары разнести на два слоя(p в одном,а n в другом) одна дорожка следует под другой - это как,допустимо?

1).А можно подробней о выравнивании шины данных по длине?Мне нужно принять 14 бит данных,LVDS,DDR(не память),частота клока 280МГц.Разброс длин дорожек бит данных(макс минус мин) - 22мм.Это нормально или ещё нужно поровнять?Какой разброс длин вообще допустим?Вроде перекос распространения всего 66 ps при периоде 1800 ps.

А вы отмоделируйте и посмотрите, какая у вас будет ширина глазка с учетом фронтов и джиттера, а потом прикиньте эти 100 ps (именно 100, потому что скорость распространения электричества в меди в лучшем случае достигает 60% скорости света из-за ненулевой индуктивности etc.) к этой ширине. Вообще 14 пар развести с выравниванием до десятки обычно нет проблем, зачем судьбу испытывать. Если вы там конечно в площадь не зажаты совсем, что аккордеон лишний не поставить.2).Конструктор не может развести диффпары по данным в одном слое,если эти диффпары разнести на два слоя(p в одном,а n в другом) одна дорожка следует под другой - это как,допустимо?

Это опять же можно в HyperLynx посмотреть, что получится, если диффпару образовывать, проводя проводники не рядом, а друг под другом. Но вообще обычно проще проводить проводники пары рядом, а уже пары сами разводить по разным слоям. Однако надо помнить, что если сделать стек слоев равномерным - то дифференциальное сопротивление внутренних слоев будет отличаться от внешних.

А вы отмоделируйте и посмотрите, какая у вас будет ширина глазка с учетом фронтов и джиттера, а потом прикиньте эти 100 ps (именно 100, потому что скорость распространения электричества в меди в лучшем случае достигает 60% скорости света из-за ненулевой индуктивности etc.) к этой ширине. Вообще 14 пар развести с выравниванием до десятки обычно нет проблем, зачем судьбу испытывать. Если вы там конечно в площадь не зажаты совсем, что аккордеон лишний не поставить.

Спасибо!Да,с площадью проблема,поколдую ещё - может что придумается.

Это опять же можно в HyperLynx посмотреть, что получится, если диффпару образовывать, проводя проводники не рядом, а друг под другом. Но вообще обычно проще проводить проводники пары рядом, а уже пары сами разводить по разным слоям. Однако надо помнить, что если сделать стек слоев равномерным - то дифференциальное сопротивление внутренних слоев будет отличаться от внешних.

Всё никак не заставлю себя сесть за освоение HyperLynx

А кто нибудь практически делал так - 10 пар шины в одном слое,а 4 пары друг под другом?

Пора себя заставить, так как даже если тут пять человек скажут вам, что вести проводники пары друг над другом - это старый испытанный поколениями способ это не будет являться поводом сделать так без модели. Потому что бывают разные микрухи, разные стэки слоев, всякие внезапные косяки, вобщем на таких частотах лучше вслепую не делать.

Пора себя заставить, так как даже если тут пять человек скажут вам, что вести проводники пары друг над другом - это старый испытанный поколениями способ это не будет являться поводом сделать так без модели. Потому что бывают разные микрухи, разные стэки слоев, всякие внезапные косяки, вобщем на таких частотах лучше вслепую не делать.

Ясно,спасибо!

Я этого честно говоря не помню, но вам это, думаю, и не потребуется - вся шина сразу даст совершеннейшую кашу. Делайте по одной линии. Другое дело что там можно потом наводки смотреть - но вы это лучше в соответствующем форуме спросите: вам там быстрее скажут, у меня просто проекта в гипере нет под рукой.

Я этого честно говоря не помню, но вам это, думаю, и не потребуется - вся шина сразу даст совершеннейшую кашу. Делайте по одной линии. Другое дело что там можно потом наводки смотреть - но вы это лучше в соответствующем форуме спросите: вам там быстрее скажут, у меня просто проекта в гипере нет под рукой.

Ясно,спасибо!

Ну не скажите..

Флеша имеет 14 лап, стандарт 1.0 позволяет работать на 10нс, шина данных камня - байт, ставите 4 шутки для 32бит - уже получаем 10/4нс на чтение в потоке, ну там +/-.

На запись в занятые сектора для уменьшения latency тоже можно поизголяться

Просто, по-моему вы не в ту сторону копаете...

Флеша имеет 14 лап, стандарт 1.0 позволяет работать на 10нс, шина данных камня - байт, ставите 4 шутки для 32бит - уже получаем 10/4нс на чтение в потоке, ну там +/-.

На запись в занятые сектора для уменьшения latency тоже можно поизголяться

Просто, по-моему вы не в ту сторону копаете...

Прошу прощения за офтоп, но мне очень интересно что за флеша такая с 14 лапами и 10нс ? интересует название микросхемы.

2 Аматер

обычная NAND флеша (ONFI стандартная которая).

Только там 14 лап для руления, а корпус вообсче на лап 48 или больше Стандарт ONFI 1.0 декларирует 10нс, второй меньше конечно

Стандарт ONFI 1.0 декларирует 10нс, второй меньше конечно

СцылкА

обычная NAND флеша (ONFI стандартная которая).

Только там 14 лап для руления, а корпус вообсче на лап 48 или больше

СцылкА

А как в HyperLynx вывести на осциллограф всю шину данных?У меня получается только по одному биту.

В HyperLynx 8.x появился модуль для моделирования DDR целиком - связки "память+ контроллер". Запустите, введите поэтапно всю информацию, потом полученные в результате моделирования файлы откройте в осциллографе - и будет Вам вся шина даных.

Для просмотра полной версии этой страницы, пожалуйста, пройдите по ссылке.