Цитата(Aner @ May 21 2014, 18:27)

А не поздно ли в нашем "болоте" ядрами заниматься? Понятно, что отстали технологически, ну оч намного. Откуда у вас вера в коммерцию для вашего ядра, вот чего не пойму.

Вы будете смеяться, но вся вера построена на одном допущении. Предистория такова - в 2003 году был перенсён код самописной файловой системы из консольного тестового проекта MS Visual Studio в задачу, исполняющуюся поверх микроядра L4Ka::Pistachio на архитектуре ia32. С учётом того, что микроядро L4 синхронное, файловая система заблокировала всю систему в момент чтения со stdin (проще говоря - система заблокировалась в ожидании нажатия клавиши на клавиатуре). Самое смешное, что все писатели операционных систем, использующих синхронные микроядра, сталкиваются с этой проблемой и решают её по своему. В результате, почти случайно, было найдено оригинальное решение развязывания синхронных вызовов в асинхронные, которое давало минимальный оверхед по ресурсам. Собственно, многолетняя убеждённость в том, что решение удачное, уникальное и никому пока ещё не пришло в голову - вот эта убеждённость и придаёт силы.

Цитата(Aner @ May 21 2014, 18:27)

В той же калифорнии, полно обанкротившихся компаниями с шикарными решениями ядер, причем у них под боком ну оч приличная топо технология. И вы туда же?

Когда работа ведётся много лет на энтузиазме и вере, когда в работу вкладываюся собственные средства, когда нет кредиторов и хозяев, диктующих что и как делать, то обанкротится сложно. Сильно рисковать желания нет, пусть со стороны это выглядит как риск, а изнутри это смотрится как целенаправленная многолетняя работа.

Кстати, собственно почему пришла идея сделать свой микропроцессор? Такие мысли были давно, но желание превратилось в намерение после переноса операционной системы "Хамелеон" с x86-32 на x86-64. В какой-то момент перенести удалось, но само микроядро L4-Pistachio работает нестабильно на 64-битах. Это очень нехорошее чувство, когда то, на что опирается ваш код, работает нестабильно, а трудозатраты на исправление чужого кода сопоставимы с трудозатратами при разработке с нуля. В общем, тут сам Бог велел забыть о "чужих" проблемах и недоработках, а сделать то, что нужно самому.

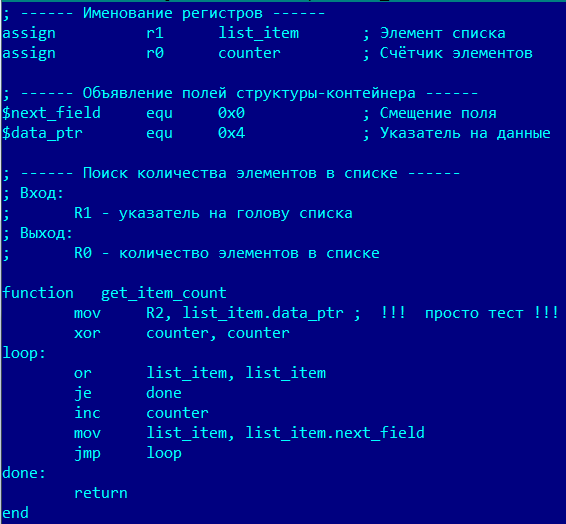

Не то, чтобы в Калифорнии никто не делал аппаратных планировщиков - такие исследования проводились разными командами, но вот чтобы кто-то реализовал аппаратно синхронное микроядро (microkernel) - такого ещё не сделал никто. Во всяком случае не сделал нечто, опирающееся на идеи из вот этой спецификации -

http://www.l4ka.org/l4ka/l4-x2-r7.pdfПростите за многословность. Я теряю самообладаение когда речь идёт об микроядре L4.