значит плагин не установлен.

Там внизу Add Exporter

До установите

Полная версия этой страницы: 2018 Вопросы начинающих

Форум разработчиков электроники ELECTRONIX.ru > Печатные платы (PCB) > Разрабатываем ПП в САПР - PCB development > Altium Designer, DXP, Protel

Подскажите, как быть:

На текущей версии платы не монтируются какие-то элементы.

Как сделать так, что бы они не попадали в BOM ?

Первая мысль - в свойствах элемента выбрать "Type - > NO BOM"

Но при этом легко ошибиться, т.к. на схеме это свойство элемента ни как не отображается.

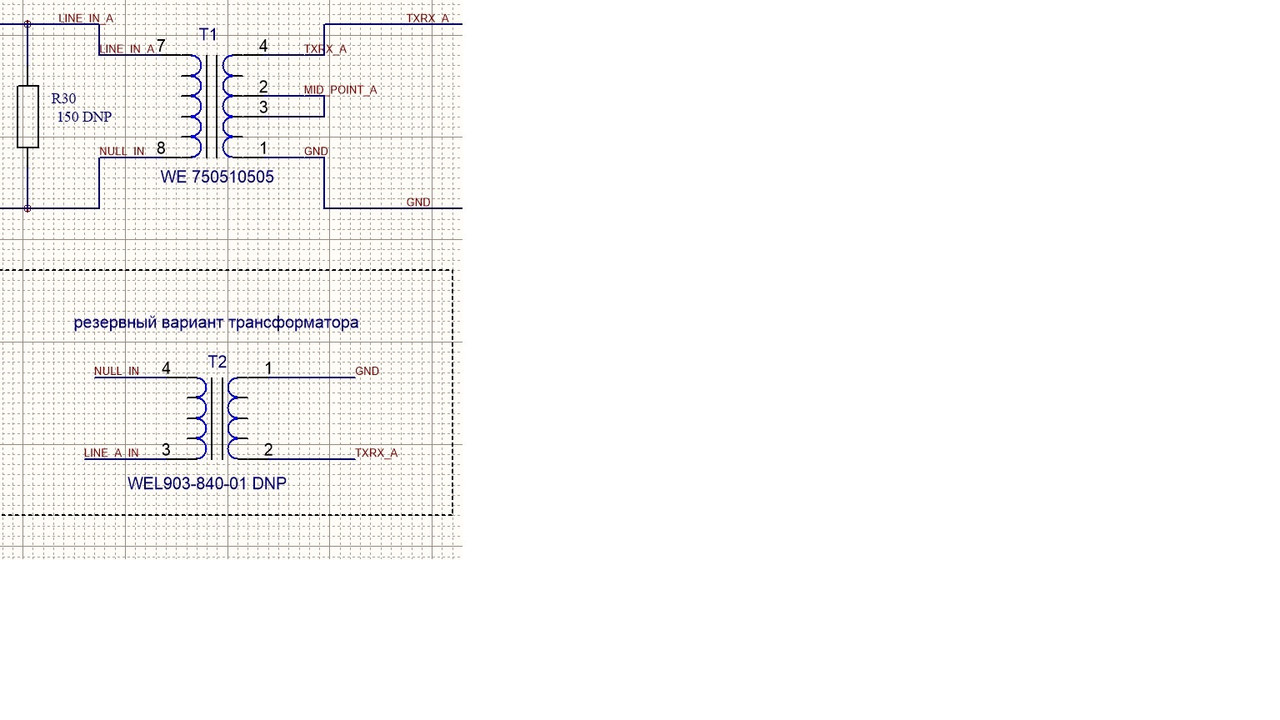

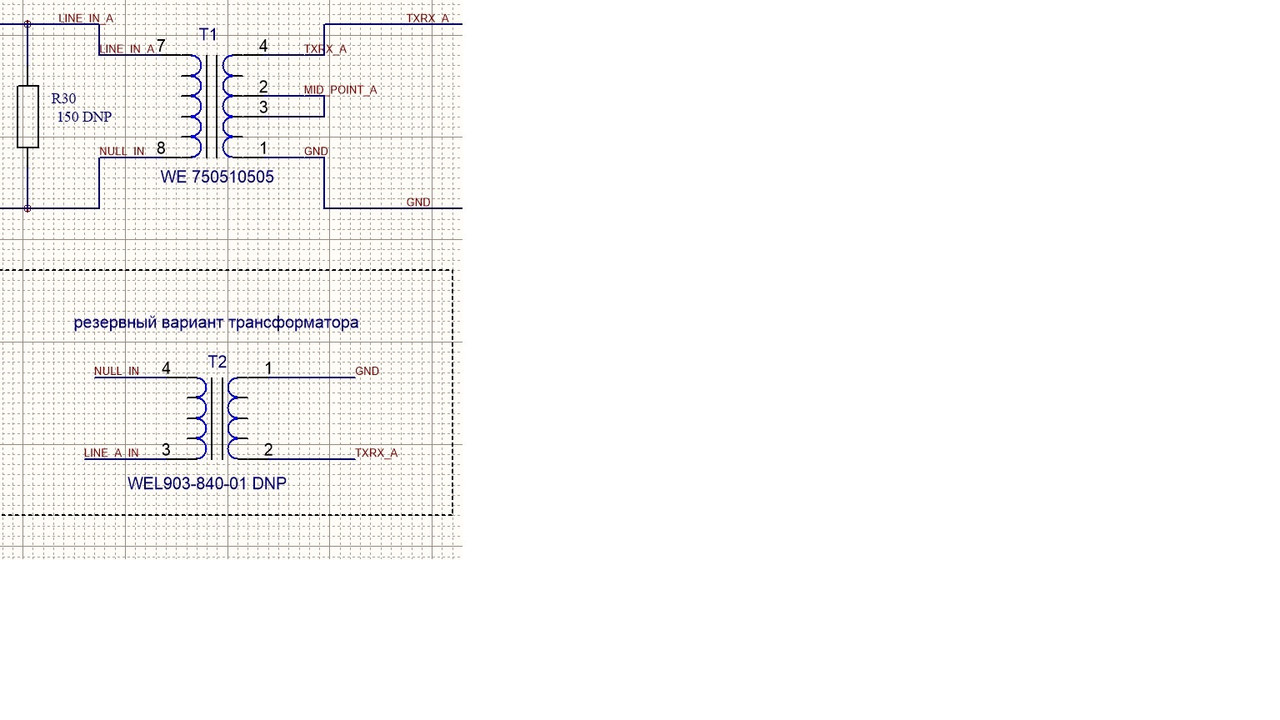

Нельзя ли назначить для элементов какое-то правило, такое, что бы по нему можно было сортировать при генерации BOM ? Что бы на схеме выглядело как-то визуально понятно, вроде этого:

На текущей версии платы не монтируются какие-то элементы.

Как сделать так, что бы они не попадали в BOM ?

Первая мысль - в свойствах элемента выбрать "Type - > NO BOM"

Но при этом легко ошибиться, т.к. на схеме это свойство элемента ни как не отображается.

Нельзя ли назначить для элементов какое-то правило, такое, что бы по нему можно было сортировать при генерации BOM ? Что бы на схеме выглядело как-то визуально понятно, вроде этого:

Решил проблему с 3D.

Задача простая: примерить получившуюся плату в корпус до изготовления. Кому-то нужно сквозное проектирование - ищите пути... SW, circuitworks, ADский вольт или ещё что-то.... Всё это громоздкое и ....

Пробовал ещё через IDF, тупо сохранить в АД в idf и открыть в SW - так не получается. SW вместо моделей рисует кубики. Все детали будут как кубики с максимальными габаритами РЭК.

Кому интересно примерить плату в корпусе в пару кликов - Я использовал Компас3Д. В AD тупо сохраняешь STEP, в Компасе открывает. Компас открывает степки от АД на ура, без ворнингов, ни чего не съезжает, не пропадает. Сохраняется вся геометрия, все надписи, Плата открывается как сборка из деталей РЭК. То что нужно!!!

Это делается через варианты.

Задача простая: примерить получившуюся плату в корпус до изготовления. Кому-то нужно сквозное проектирование - ищите пути... SW, circuitworks, ADский вольт или ещё что-то.... Всё это громоздкое и ....

Пробовал ещё через IDF, тупо сохранить в АД в idf и открыть в SW - так не получается. SW вместо моделей рисует кубики. Все детали будут как кубики с максимальными габаритами РЭК.

Кому интересно примерить плату в корпусе в пару кликов - Я использовал Компас3Д. В AD тупо сохраняешь STEP, в Компасе открывает. Компас открывает степки от АД на ура, без ворнингов, ни чего не съезжает, не пропадает. Сохраняется вся геометрия, все надписи, Плата открывается как сборка из деталей РЭК. То что нужно!!!

На текущей версии платы не монтируются какие-то элементы.

Как сделать так, что бы они не попадали в BOM ?

Как сделать так, что бы они не попадали в BOM ?

Это делается через варианты.

Вот почему и нужно все рисовать в SW.

Этого мало, т.е. если вы нарисовали в SW сами деталь и откроете свои idf - ни какие модели SW не подтянет. Прежде нужно бубном стучать. У меня часть элементов нарисована в SW и сохранена как степ. Ни один компонент не порисовался. Нужно бубном что-то сопоставлять. Более того - я степку ПП сохранил на флешку дома, на работе открыл - где тут мои солиды и степ модели отдельных компонентов? Нету! Нужно таскать на флешке все исходники.... на работе делать сопоставления.... нееее... это не наш метод.Тем более часть компонентов с 3dcontentcentral, часть компонентов с официальных библиотек от Altium-а ( а там вообще нет отдельно 3д на деталь, только *.libPcb), часть деталей с библиотек от производителей микросхем, часть деталей вообще с библиотеки колеги... бывшего.

Альтиумом тупо на любом пк сохранил ПП в степ, на любом пк открыл ПП в компасе. Ни какие исходные степ/sw не нужны.

А можно подробнее ? В каком это меню и как называется по-английски, что бы найти уроки ?

я сам не делал. В схематике есть меню Project->Variants...

в PCB есть см рисунок. В схематике тоже вверху выбор варианта. При выборе варианта в схеме не нужные УГО будут зачеркнуты красным. Не надо писать что-то как увас "Это не ставить в таком варианте".

При генерации бом, выбераеете вариант и не нужных деталей не будет.

вот вам зацепка

я сам не делал. В схематике есть меню Project->Variants...

в PCB есть см рисунок. В схематике тоже вверху выбор варианта. При выборе варианта в схеме не нужные УГО будут зачеркнуты красным. Не надо писать что-то как увас "Это не ставить в таком варианте".

При генерации бом, выбераеете вариант и не нужных деталей не будет.

вот вам зацепка

в PCB есть см рисунок. В схематике тоже вверху выбор варианта. При выборе варианта в схеме не нужные УГО будут зачеркнуты красным. Не надо писать что-то как увас "Это не ставить в таком варианте".

При генерации бом, выбераеете вариант и не нужных деталей не будет.

вот вам зацепка

Да там все прозаично.

Настраивать только нудно и по мне, так не дружественно.

Но все работает давно и неплохо

Ну это да. Только теперь вопрос к знатокам. Где этот бубен. Как и где сопоставить STEP и компоненты Солида.

Если хотите идти пропой idf, то бубен - это CircuitWorks, мануал можно глянуть тут

значит плагин не установлен.

Там внизу Add Exporter

До установите

Там внизу Add Exporter

До установите

Я там уже смотрел и не нашел.

Подскажите, как называется и где взять плагин для экспорта из AD в PCAD?

UPD: Нашел на официальном сайте Альтиума https://designcontent.live.altium.com/Plugi...rter_PCAD_ASCII

Не могу пройти регистрацию, чтобы установить.

Может кто-нить скинуть этот плагин на мыло evgen_f[сбк]ardf.ru?

quote name='musa' date='Jun 29 2018, 06:54' post='1569746']

Ну это да. Только теперь вопрос к знатокам. Где этот бубен. Как и где сопоставить STEP и компоненты Солида.

[/quote]

Передача через IDF, это плохой вариант (от слова СОВСЕМ). Может, когда будет возможность экспорта в версии IDF-4, что-нибудь изменится. Нужно создавать свою IDF-библиотеку, причём, в SW-формате. Более того, двигать элементы по плате нереально (теоретически можно, через изменение элементов в библиотеке, практически - нет). Нормальный путь, - это делать библиотеки футпринтов с подключёнными STEP-моделями или, ещё лучше, деталями в формате SW, а потом делать экспорт в Парасолид. Далее, - любая трёхмерка поймёт. Компоненты лучше делать самим в SW в виде детали, а не сборки (ну, или в друго трёхмерке, тогда сохранять в Степ), так, чтобы точка привязки в SW совпадала с нулевой координатой в футпринте AD.

Ну это да. Только теперь вопрос к знатокам. Где этот бубен. Как и где сопоставить STEP и компоненты Солида.

[/quote]

Передача через IDF, это плохой вариант (от слова СОВСЕМ). Может, когда будет возможность экспорта в версии IDF-4, что-нибудь изменится. Нужно создавать свою IDF-библиотеку, причём, в SW-формате. Более того, двигать элементы по плате нереально (теоретически можно, через изменение элементов в библиотеке, практически - нет). Нормальный путь, - это делать библиотеки футпринтов с подключёнными STEP-моделями или, ещё лучше, деталями в формате SW, а потом делать экспорт в Парасолид. Далее, - любая трёхмерка поймёт. Компоненты лучше делать самим в SW в виде детали, а не сборки (ну, или в друго трёхмерке, тогда сохранять в Степ), так, чтобы точка привязки в SW совпадала с нулевой координатой в футпринте AD.

Как-то так:

Нажмите для просмотра прикрепленного файла

Нажмите для просмотра прикрепленного файла

У меня так, нет такой галки. ад16

Обновите версию. В последней точно есть.

16 уже не держу

16 уже не держу

Да, у меня 17.1.9.

Насчёт Компаса взял на заметку - но смежникам-"механикам" нужен солидворкс и никак иначе.

Насчёт Компаса взял на заметку - но смежникам-"механикам" нужен солидворкс и никак иначе.

Подскажите, пожалуйста, как избавиться от автоматических вычислений в поле Comment при создании компонента.

Т.е. ввожу я part number разъёма 3-6318490-6, Альтиум считает это математическим выражением и меняет на -6318481

Понятно, что можно написать в кавычках но это как-то некрасиво. Экселевский вариант с ' не работает.

Т.е. ввожу я part number разъёма 3-6318490-6, Альтиум считает это математическим выражением и меняет на -6318481

Понятно, что можно написать в кавычках но это как-то некрасиво. Экселевский вариант с ' не работает.

Не используйте знак "="

У себя такого не наблюдаю.

Все отображается нормально

Все отображается нормально

Сбросьте все настройки в Default

Сбросил, эффект нулевой. Ну да ладно, сделал в 15-й.

Добрый день! возникла проблема, в проекте обозначения элементов в PCB, не соответствует обозначению в Sch.

Т.е. Альтиум начал считать, что микра TO-92A это например HSOP8, перепривязал привязки. В конечном счете, вся плата перепуталась. При попытках переименовать компоненты и переимпортировать из схематика в писиби, пишет ошибки типа:

"Class Document Source Message Time Date No.

[Error] Pover02.SchDoc Compiler Duplicate Component Designators R6 (R48) at 532.16mm,445.04mm and 318.5mm,511mm 18:12:30 05.07.2018 3

"

Подскажите, что делать?

Т.е. Альтиум начал считать, что микра TO-92A это например HSOP8, перепривязал привязки. В конечном счете, вся плата перепуталась. При попытках переименовать компоненты и переимпортировать из схематика в писиби, пишет ошибки типа:

"Class Document Source Message Time Date No.

[Error] Pover02.SchDoc Compiler Duplicate Component Designators R6 (R48) at 532.16mm,445.04mm and 318.5mm,511mm 18:12:30 05.07.2018 3

"

Подскажите, что делать?

Project/Copmponent Link

Пересвязать по обозначению

А последние вообще к схеме имеет отношение только--- дублирование Designator

Или сбросите дубли или полностью пере аннотация проекта

Пересвязать по обозначению

А последние вообще к схеме имеет отношение только--- дублирование Designator

Или сбросите дубли или полностью пере аннотация проекта

Кстати о дублях.

Достался мне проект по наследству.

Возможно ли запретить подобное в проектах или найти все места, где на одной цепи стоят разные имена?

Нажмите для просмотра прикрепленного файла

Достался мне проект по наследству.

Возможно ли запретить подобное в проектах или найти все места, где на одной цепи стоят разные имена?

Нажмите для просмотра прикрепленного файла

Кстати о дублях.

Достался мне проект по наследству.

Возможно ли запретить подобное в проектах или найти все места, где на одной цепи стоят разные имена?

Нажмите для просмотра прикрепленного файла

Достался мне проект по наследству.

Возможно ли запретить подобное в проектах или найти все места, где на одной цепи стоят разные имена?

Нажмите для просмотра прикрепленного файла

Запретить нельзя

Найти можно

Начнем с того что это просто не должно быть.

Ну это не совсем так.

Иногда используют ка фичу (но я против двойных наименований-- они путуют)

Но попадался иерархический проект с каналами. Причем соединены были последовательно.

Для того чтобы красиво обойти и правильно передать сигналы --- там как раз такое было сделано.

По связям получилось красиво -- слов нет.

Но сточки зрения читаемости схемы-- не совсем.

Что они хотели сделать я понял сразу. Особенно имея PCB. Но в идентичном проекте я не смог соединить правильно последовательные каналы (и отказался от них), а они запросто решили эту схемотехничекую проблему.

Спасибо! ))

Там предупреждений на пару экранов и я просмотрел нужную строчку.

Увидел тут сообщение про дубли и решил спросить. А уж зная, что оно там есть... )))

Там предупреждений на пару экранов и я просмотрел нужную строчку.

Увидел тут сообщение про дубли и решил спросить. А уж зная, что оно там есть... )))

Правильно спросили.

Altium позволяет все (что с точки зрения PCAD просто не допустимо)

Но при этом находит и сообщает что не так. А дело разработчика устранить, или это он так "задумал".

В таком подходе, как всегда, есть плюсы и МИНУСЫ

Altium позволяет все (что с точки зрения PCAD просто не допустимо)

Но при этом находит и сообщает что не так. А дело разработчика устранить, или это он так "задумал".

В таком подходе, как всегда, есть плюсы и МИНУСЫ

Да но нужно с большой осторожностью к этому подходить чтобы не спутать случайное замыкание и соединение сделаное специально. В иерархических проектах это используется но там свой механизм этих соединений.

Да. Именно так.

Поэтому предпочитаю делать схему одновременно с топологий.

При синхронизации можно заметит случайно сделанные на схеме замыкания.

Там предупреждений на пару экранов и я просмотрел нужную строчку.

Если хотите гарантированно найти все подобные места на схеме, в настройках проекта на вкладке Error Reporting ставьте режим оповещения Fatal Error о нарушениях типа Nets with multiplie names. И запустите компиляцию. Тогда они будут красными в окне сообщений и не затеряются в желтой массе прочих предупреждений.

.

Подскажите пожалуйста, как сказать чтобы в ECO не попадали некоторые добавленные компоненты. У меня нарисованы 2 варианта реализации, чисто для себя.

Так вот при обновлении PCB проекта, этот трансформатор T2 постоянно попадает в ECO. Как это отключить, не глобальной настройкой для всех компонентов которая в Project Options?

Так вот при обновлении PCB проекта, этот трансформатор T2 постоянно попадает в ECO. Как это отключить, не глобальной настройкой для всех компонентов которая в Project Options?

Подскажите пожалуйста, как сказать чтобы в ECO не попадали некоторые добавленные компоненты. У меня нарисованы 2 варианта реализации, чисто для себя.

Так вот при обновлении PCB проекта, этот трансформатор T2 постоянно попадает в ECO. Как это отключить, не глобальной настройкой для всех компонентов которая в Project Options?

Так вот при обновлении PCB проекта, этот трансформатор T2 постоянно попадает в ECO. Как это отключить, не глобальной настройкой для всех компонентов которая в Project Options?

Сменить тип компонента:

Нажмите для просмотра прикрепленного файла

Как сделать чтобы Via подключались автоматически у цепи полигона? Ставлю новые переходные на полигон, а они никуда не подключены.

Как сделать чтобы Via подключались автоматически у цепи полигона? Ставлю новые переходные на полигон, а они никуда не подключены.

Никто более умного не предложил :-) Я копирую via, подключенное к нужной net, и затем вставляю Edit - Paste Special с установленным чекбоксом "Keep net name" (E - A - Enter).

С какого то момента не сложная двухслойная плата стала дико тормозить при перемещении компонента.

OnlineDRC выключил, не помогает

В правилах тоже снял галки.

И онлайнDRC натсройки там же многое позакрывал.

Тормозит.

Что удивительно, онлайн проверка выключена, но почему то не дает при перемещении проходить компонентом по другому, то есть наложение проверяется. Как?

После сдвига компонента с горем пополам, комп все равно замирает, на пару секунд и внизу проносится надпись analizing net с перебором цепей

OnlineDRC выключил, не помогает

В правилах тоже снял галки.

И онлайнDRC натсройки там же многое позакрывал.

Тормозит.

Что удивительно, онлайн проверка выключена, но почему то не дает при перемещении проходить компонентом по другому, то есть наложение проверяется. Как?

После сдвига компонента с горем пополам, комп все равно замирает, на пару секунд и внизу проносится надпись analizing net с перебором цепей

Непонятно зачем портироватьмодели из AD в SW?

Например, для того, что бы сделать корпус, котрый "обливает" плату или разные хитрые крепежные детали...

Как сделать чтобы Via подключались автоматически у цепи полигона? Ставлю новые переходные на полигон, а они никуда не подключены.

Копируйте виас на пад, который подключен к той же цепи, что и полигон.

С какого то момента не сложная двухслойная плата стала дико тормозить при перемещении компонента.

такая ерунда была, когда на плате присутствовал логотип производителя, выполненный в виде массива линиий. его прорисовывать - непомерная нагрузка на AD, даже если он никуда не перетаскивается, а сидит себе где-то и не отсвечивает.

такая ерунда была, когда на плате присутствовал логотип производителя, выполненный в виде массива линиий. его прорисовывать - непомерная нагрузка на AD, даже если он никуда не перетаскивается, а сидит себе где-то и не отсвечивает.

нет, тут что то другое.

не дает произвольно ставить компонент. значит DRC все равно включено как то хитрым способом

Между "сильно тормозит" и "не дает произвольно ставить" -- большая разница.

Про первое вам сказали одну из причин. Там им может быть несколько.

Про второе -- стоит флаг расталкивания компонентов. Установите в игнорирование -- буде ставить как угодно

Про первое вам сказали одну из причин. Там им может быть несколько.

Про второе -- стоит флаг расталкивания компонентов. Установите в игнорирование -- буде ставить как угодно

Где меняется порядок отрисовки полигонов? Рисую один полигон поверх другого, он не прорисовывается. Т.е. его как буд - то нет. Помогите пожалуйста.

Не должно быть ни одного предупреждения. Проект должен проверяться/компиляться в ноль, т.е. ни одной ошибки, ни одного предупреждения. За каждым ворнингом прячутся баги.

Как-правило так, но всё-же не всегда и не везде.

Например предупреждение "Подключение скрытых выводов компонента к цепи.." вполне допустимы, если в библиотечных компонентах имеются таковые. А это весьма распространённое явление, особенно для цепей питания.

Просто надо в проекте настраивать типы оповещений по максимуму на ошибки. А предупреждений оставлять по-минимуму. И лишь те, причины появления которых в конкретном проекте ты сам реально понимаешь и прогнозируешь возможность их появления: да, они могут быть вот такие потому, что вот в этом месте у меня сделано так-то.

Лучше, конечно, задавать правила максимально жёстко. Я для этого практически на всё ставлю Fatal error.

Как-правило так, но всё-же не всегда и не везде.

Например предупреждение "Подключение скрытых выводов компонента к цепи.." вполне допустимы, если в библиотечных компонентах имеются таковые. А это весьма распространённое явление, особенно для цепей питания.

Просто надо в проекте настраивать типы оповещений по максимуму на ошибки. А предупреждений оставлять по-минимуму. И лишь те, причины появления которых в конкретном проекте ты сам реально понимаешь и прогнозируешь возможность их появления: да, они могут быть вот такие потому, что вот в этом месте у меня сделано так-то.

Лучше, конечно, задавать правила максимально жёстко. Я для этого практически на всё ставлю Fatal error.

Например предупреждение "Подключение скрытых выводов компонента к цепи.." вполне допустимы, если в библиотечных компонентах имеются таковые. А это весьма распространённое явление, особенно для цепей питания.

Просто надо в проекте настраивать типы оповещений по максимуму на ошибки. А предупреждений оставлять по-минимуму. И лишь те, причины появления которых в конкретном проекте ты сам реально понимаешь и прогнозируешь возможность их появления: да, они могут быть вот такие потому, что вот в этом месте у меня сделано так-то.

Лучше, конечно, задавать правила максимально жёстко. Я для этого практически на всё ставлю Fatal error.

Их не должно быть. Если они важны-- их нужно смотреть и устранять как Fatal так и warning

Если не важны-- они отключаются.

Как крайность-- их можно все отключить и проект будет без ошибок.

Но что важно. что нет дело только разработчика.

Цитата

Как-правило так, но всё-же не всегда и не везде.

Например предупреждение "Подключение скрытых выводов компонента к цепи.."

Не хотел отвечать, ибо не устраивать спор. Но поддержу ВладимираНапример предупреждение "Подключение скрытых выводов компонента к цепи.."

Я не различаю ворнинг и ошибку, а тем более error и Fatal error. Вообще, что такое Fatal error? Чем он отличается от error?

Проект должен копиляться или проверять в ноль. Ни каких ворнингов и ерроров. Либо настраивайте правила, чтоб не было ворнинга (например на D3 нога 4 должна быть так и так), либо устраняйте условия ворнинга.

Тем более у Panych ворнингов было ПАРУЭКРАНОВ!!!

ps

Цитата

Например предупреждение "Подключение скрытых выводов компонента к цепи.." вполне допустимы, если в библиотечных компонентах имеются таковые. А это весьма распространённое явление

Это весьма распространённое явление выстрела себе в ногу в АД. Забудьте про скрытые выводы. Их не должно быть. Схема может быть транслирована в пдф. Там скрытые выводы не видны. Да и в АД этот "финт" ухудшает читаемость. смотришь в схему и не видно пинов/цепей. Может получитсья так, что ногу нужно зацепить на AGND, а она зацепилась скрытым пином на GND, а может вообще быть NoNet. Попробуйте сделайте на микросхме все пины срытые.... на резисторах скрытые.... на кондёрах.... Как ваша схема будет выглядеть?

Ни чего не должно быть неявного. Всё должно быть очевидно и прозрачно!!!

pps Если вы любите делать

Для просмотра полной версии этой страницы, пожалуйста, пройдите по ссылке.